Risc

The information for these notes is taken from two papers describing the RISC architecture. For more detailed information on RISC, see the following:

D. A. Patterson and C. H. Sequin, "A VLSI RISC," Computer 15(9):8-21 (September 1982).

D. A. Patterson and C. H. Sequin, "RISC I: A Reduced Instruction Set VLSI Computer,"

Proceedings of the 6th Annual Symposium on Computer Architecture (1981), pp 443-456.

RISC is an attempt to decrease the number of different machine instructions in a computer architecture. It has been found that in regular architectures (such as the VAX), the number of instructions used by the compiler writer is a small subset of the total number of instructions available on the machine. RISC architectures attempt to find that small subset of instructions needed by the compiler writer so programs can execute efficiently without the overhead of numerous instructions not used.

1. Basic Architecture

Negative numbers are represented using two's-complement notation. The basic RISC architecture consists of memory, a set of registers, and a set of instructions. Memory is byte addressable. Every procedure has a set of 32 registers from which to work. Registers are named R0 through R31.

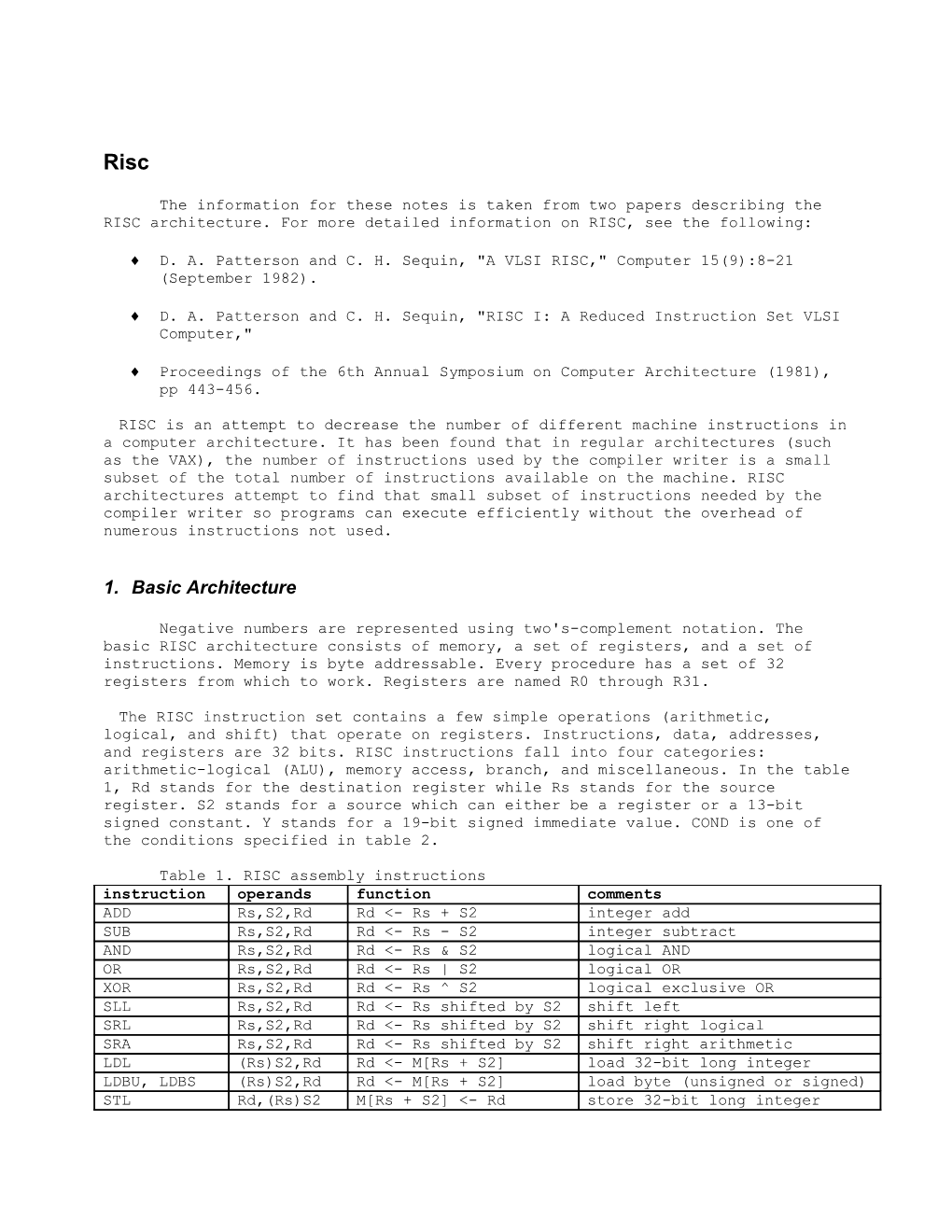

The RISC instruction set contains a few simple operations (arithmetic, logical, and shift) that operate on registers. Instructions, data, addresses, and registers are 32 bits. RISC instructions fall into four categories: arithmetic-logical (ALU), memory access, branch, and miscellaneous. In the table 1, Rd stands for the destination register while Rs stands for the source register. S2 stands for a source which can either be a register or a 13-bit signed constant. Y stands for a 19-bit signed immediate value. COND is one of the conditions specified in table 2.

Table 1. RISC assembly instructions instruction operands function comments ADD Rs,S2,Rd Rd <- Rs + S2 integer add SUB Rs,S2,Rd Rd <- Rs - S2 integer subtract AND Rs,S2,Rd Rd <- Rs & S2 logical AND OR Rs,S2,Rd Rd <- Rs | S2 logical OR XOR Rs,S2,Rd Rd <- Rs ^ S2 logical exclusive OR SLL Rs,S2,Rd Rd <- Rs shifted by S2 shift left SRL Rs,S2,Rd Rd <- Rs shifted by S2 shift right logical SRA Rs,S2,Rd Rd <- Rs shifted by S2 shift right arithmetic LDL (Rs)S2,Rd Rd <- M[Rs + S2] load 32-bit long integer LDBU, LDBS (Rs)S2,Rd Rd <- M[Rs + S2] load byte (unsigned or signed) STL Rd,(Rs)S2 M[Rs + S2] <- Rd store 32-bit long integer STB Rd,(Rs) M[Rs + S2] <- Rd store byte JMP COND,S2(Rs) pc <- Rs + S2 if COND conditional jump CALL Rd,S2(Rs) Rd <- pc, pc <- Rs+S2 function call CWP <- CWP–1 RET Rd,S2 pc <- Rd+S2, function call return CWP <- CWP+1 LDHI Rd,Y Rd<31:13> <- Y, load high immediate Rd<12:0> <- 0 HALT stop execution

Only load and store instructions can access memory.

Branch instructions include call, return, and conditional jumps. The conditional instructions are the standard set used originally in the PDP-11 and found in many 16-bit microprocessors today.

Table 2. Conditions for jumps mnemonic meaning unc unconditional equ equal to zero neq not equal to zero lt less than zero leq less than or equal to zero gt greater than zero geq greater than or equal to zero

2. Register Windows

In a RISC architecture, the overhead for a procedure call must be as low as possible -- perhaps no more than a few jumps. The RISC register window scheme comes close to this goal. At the same time, this scheme also reduces the number of accesses to data memory.

In conventional architectures, using procedures involves two groups of time-consuming operations: saving or storing registers on each call or return, and passing parameters and results to and from the procedure. In the RISC machine, each procedure call results in a new set of registers being allocated, from a large register bank, for use by the new procedure. Each procedure has registers that overlap with the previous and subsequently-called procedures. The return just resets a pointer, restoring the old set. Some of the 32 registers are not reallocated on each procedure call. These registers (RO through R9) are called global registers. It should be noted that register zero (RO) always contains a zero.

Parameters to be passed to a called procedure are simply placed in overlapping registers. In other machines, parameters are usually passed on the stack, and the calling procedure uses a register (frame pointer) that points to the beginning of the parameters (and also the end of the locals). Thus, all references to parameters are indexed references to memory. The RISC approach partitions the set of window registers (10-31) into three sections defined by their respective overlap. Every procedure sees the set of registers shown in the following table. Table 3. Naming of RISC registers Register group name register numbers overlap HIGH R26 through R31 caller’s LOW regs Local R16 through R25 -- no overlap -- LOW R10 through R15 called HIGH regs Global R0 through R9 -- all procs share --

High registers 26 through 31 contain parameters passed from "above" the current procedure -- that is from the calling procedure. Local registers 16 through 25 are used for local scalar storage. Low registers 10 through 15 are used for temporaries and parameters passed to the procedure "below" the current procedure (the called procedure). On each procedure call a new set of registers, numbered 10-31, is allocated. The low register of the "caller" become the high register of the "callee" because of the hardware overlap between subsequent register windows. Thus without moving information, parameters in registers 10-15 appear in registers 25-31 of the called window. The following figure illustrates this approach for the case where procedure A calls procedure B, which calls procedure C.

Physical register bank R26 – R31 Procedure A

R16 – R25

R10 – R15 Procedure B R26 – R31

R16 – R25

Procedure C R10 – R15 R26 – R31

R16 – R25

R10 – R15

R0 – R9 R0 – R9 R0 – R9 3. Supplied Routines

Some useful routines are provided by a BIOS or interpreter and are shown below. These routines deal with arithmetic operations not available in the RISC machine, input, and output. These are available to you via a subroutine call to a specific address. You must know where the subroutine is located, where to place input parameters, and where the routine places the results. To use the interpreter-supplied routines, you must load user code at memory address 200 or higher. This reserves lower memory locations for these routines.

Multiply Divide address – 150 address - 151 R26 - return address R26 – return address R27 – result R27 - quotient R28 – multiplicand R28 – remainder R29 – multiplier R29 - dividend R30 - divisor CrLf Carriage return-line feed address - 152 R26 - return address

ReadLn address - 156 R26 - return address

WriteChar address - 153 R26 - return address R27 - ASCII character

ReadChar address - 157 R26 — return address R27 — memloc to place character

WriteInteger address - 154 R26 - return address R27 - integer

ReadInteger address - 158 R26 — return address R27 - memloc to place integer

WriteString address - 160 R26 - return address R27 - address of string