Extracting Keys from Second Generation Zigbee Chips

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Ember Em35x Development Kit User Guide

UG113 EM34X DEVELOPMENT KIT USER’S GUIDE Contents 1 About This Guide ............................................................................................................................................ 4 1.1 Purpose ................................................................................................................................................... 4 1.2 Audience .................................................................................................................................................. 4 1.3 Documentation Conventions..................................................................................................................... 4 2 Introducing the EM34x Development Kit .......................................................................................................... 4 2.1 Overview .................................................................................................................................................. 4 2.2 Development Kit Contents ........................................................................................................................ 5 2.3 Hardware Requirements .......................................................................................................................... 5 2.4 Software Requirements ............................................................................................................................ 5 2.5 Hardware ................................................................................................................................................ -

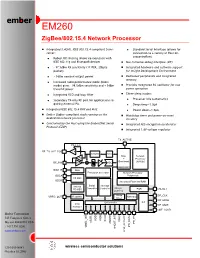

EM260 Zigbee/802.15.4 Network Processor

EM260 ZigBee/802.15.4 Network Processor Integrated 2.4GHz, IEEE 802.15.4-compliant trans- • Standard Serial Interface (allows for ceiver: connection to a variety of Host mi- crocontrollers) • Robust RX filtering allows co-existence with IEEE 802.11g and Bluetooth devices Non-intrusive debug interface (SIF) • - 97.5dBm RX sensitivity (1% PER, 20byte Integrated hardware and software support packet) for InSight Development Environment • + 3dBm nominal output power Dedicated peripherals and integrated memory • Increased radio performance mode (boost mode) gives – 98.5dBm sensitivity and + 5dBm Provides integrated RC oscillator for low transmit power power operation • Integrated VCO and loop filter Three sleep modes: • Secondary TX-only RF port for applications re- • Processor idle (automatic) quiring external PA. • Deep sleep—1.0μA Integrated IEEE 802.15.4 PHY and MAC • Power down—1.0μA Ember ZigBee-compliant stack running on the Watchdog timer and power-on-reset dedicated network processor circuitry Controlled by the Host using the EmberZNet Serial Integrated AES encryption accelerator Protocol (EZSP) Integrated 1.8V voltage regulator TX_ACTIVE PA select RF_TX_ALT_P,N PA SYNTH DAC MAC Network PA + Processor Baseband (XAP2b) RF_P,N LNA IF ADC PacketTrace BIAS_R Bias Encryption acclerator Network Processor OSCA Peripherals HF OSC OSCB Integrated Flash and RAM Internal Serial Interrupt Always RC-OSC Controller Controller POR nRESET powered Sleep Regulator Watchdog SIF_CLK VREG_OUT timer SIF_MISO IO Controller SIF Chip SIF_MOSI manager nSIF_LOAD Ember Corporation 343 Congress Street MOSI MISO SCLK SDBG nSSEL Boston MA 02210 USA nWAKE PTI_EN PTI_DATA +1 617.951.0200 nSSEL_INT nHOST_INT www.ember.com LINK_ACTIVITY 120-1003-000G wireless semiconductor solutions October 10, 2006 EM260 General Description The EM260 integrates a 2.4GHz, IEEE 802.15.4-compliant transceiver with a 16-bit network processor (XAP2b core) to run EmberZNet, the Ember ZigBee-compliant network stack. -

Zigbee 802.15.4 Network Processor

SN260 ZigBee® 802.15.4 network processor Features ■ Controlled by the Host using the EmberZNet™ Serial Protocol (EZSP) ■ Integrated 2.4GHz, IEEE 802.15.4-compliant – Standard SPI or UART interfaces allow for transceiver: connection to a variety of Host – Robust RX filtering allows co-existence microcontrollers with IEEE 802.11g and Bluetooth devices ■ Non-intrusive debug interface (SIF) – –99 dBm RX sensitivity (1% PER, 20-byte ■ packet) Integrated hardware and software support for InSight™ Development Environment – +2.5 dBm nominal output power ■ – Increased radio performance mode (Boost Provides integrated RC oscillator for low power mode) gives –100 dBm sensitivity and operation +4.5 dBm transmit power ■ Three sleep modes: – Integrated VCO and loop filter – Processor idle (automatic) – Secondary TX-only RF port for applications – Deep sleep—1.0µA requiring external PA. – Power down—1.0µA ■ Integrated IEEE 802.15.4 PHY and MAC ■ Watchdog timer and power-on-reset circuitry ■ Dedicated peripherals and integrated memory ■ Integrated AES encryption accelerator ■ Ember ZigBee®-compliant stack running on ■ Integrated 1.8V voltage regulator the dedicated network processor Obsolete Product(s) - Obsolete Product(s) March 2009 Rev 4 1/47 www.st.com 1 Contents SN260 Contents 1 Abbreviations and acronyms . 5 2 References . 6 3 General description . 7 4 Pin assignment . 8 5 Top-level functional description . 12 6 Functional description . 14 6.1 Receive (RX) path . 14 6.1.1 RX baseband . 14 6.1.2 RSSI and CCA . 14 6.2 Transmit (TX) path . 15 6.2.1 TX baseband . 15 6.2.2 TX_ACTIVE signal . 15 6.3 Integrated MAC module . -

UG103.4: HAL Fundamentals

UG103.4: HAL Fundamentals Silicon Labs HAL (Hardware Abstraction Layer) is program code between a system’s hardware and its software that provides a KEY POINTS consistent interface for applications that can run on several differ- • Provides information on how the HAL is ent hardware platforms. The HAL is designed for developers us- organized, including naming conventions, ing EmberZNet PRO with the EFR32MG family of products. API files, and directory structure. • Includes an overview of each of the main Silicon Labs’ Fundamentals series covers topics that project managers, application de- subsections of the HAL functionality. signers, and developers should understand before beginning to work on an embedded • Describes how to adapt the HAL to your networking solution using Silicon Labs chips, networking stacks such as EmberZNet specific hardware and application PRO or Silicon Labs Bluetooth®, and associated development tools. The documents requirements. can be used as a starting place for anyone needing an introduction to developing wire- less networking applications, or who is new to the Silicon Labs development environ- ment. silabs.com | Building a more connected world. Rev. 1.4 UG103.4: HAL Fundamentals Introduction 1. Introduction The Hardware Abstraction Layer (HAL) is program code between a system’s hardware and its software that provides a consistent inter- face for applications that can run on several different hardware platforms. To take advantage of this capability, applications should ac- cess hardware through the API provided by the HAL, rather than directly. Then, when you move to new hardware, you only need to update the HAL. In some cases, due to extreme differences in hardware, the HAL API may also change slightly to accommodate the new hardware. -

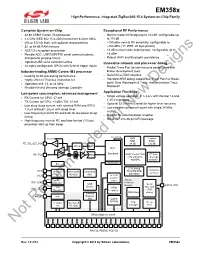

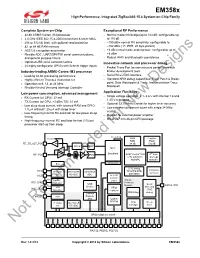

Em358x High-Performance, Integrated Zigbee/802.15.4 System-On-Chip Family

EM358x High-Performance, Integrated ZigBee/802.15.4 System-on-Chip Family Complete System-on-Chip Exceptional RF Performance - 32-bit ARM® Cortex -M3 processor - Normal mode link budget up to 103 dB; configurable up - 2.4 GHz IEEE 802.15.4-2003 transceiver & lower MAC to 110 dB - 256 or 512 kB flash, with optional read protection - –100 dBm normal RX sensitivity; configurable to - 32 or 64 kB RAM memory –102 dBm (1% PER, 20 byte packet) - AES128 encryption accelerator - +3 dB normal mode output power; configurable up to - Flexible ADC, UART/SPI/TWI serial communications, +8 dBm and general purpose timers - Robust Wi-Fi and Bluetooth coexistence Optional USB serial communications - Innovative network and processor debug 24 highly configurable GPIOs with Schmitt trigger inputs - - Packet Trace Port for non-intrusive packet trace with Industry-leading ARM® Cortex -M3 processor Ember development tools - Leading 32-bit processing performance - Serial Wire/JTAG interface - Highly efficient Thumb-2 instruction set - Standard ARM debug capabilities: Flash Patch & Break- - Operation at 6, 12, or 24 MHz point; Data Watchpoint & Trace; InstrumentationDesigns Trace Macrocell - Flexible Nested Vectored Interrupt Controller Application Flexibility Low power consumption, advanced management - Single voltage operation: 2.1–3.6 V with internal 1.8 and - RX Current (w/ CPU): 27 mA 1.25 V regulators - TX Current (w/ CPU, +3 dBm TX): 31 mA - Optional 32.768 kHz crystal for higher timer accuracy - Low deep sleep current, with retained RAM and GPIO: - Low -

ARM® Cortex® -M3 & M4 MCU Architecture

ARM® Cortex ® -M3 & M4 MCU Architecture Introduction Many embedded developers are familiar with the ARM Cortex processor architecture, but few have the opportunity to become intimately acquainted enough of this popular architecture to take full advantage of its unique features and capabilities. This is especially true for the new ARM Cortex-M4 processor, which boasts an improved architecture, native digital signal processing (DSP) capabilities and an optional floating-point accelerator, which a savvy programmer or hardware engineer can exploit to their ad- vantage. Let’s take a closer look at some of the more interesting (and often-overlooked) features found in Cortex-M3 based microcontrollers (MCUs) as well as new M4 variants. Since many target applications for Cortex-M based MCUs are portable and derive their power from bat- teries or energy harvesting systems, most of the ideas we will explore involve techniques for reducing a design’s overall energy consumption. In many cases, however, these energy conservation techniques are also helpful tools for designing processor-optimized applications that provide: • More cost-effective solutions • More processing margin available for upgrades and new features • Performance and features that help products stand out in crowded markets. ARM Cortex Basics Much like the original 16-bit processor cores created by Advanced RISC Machines (ARM) in the 1980s, the ARM Cortex series is based on a Harvard-style RISC machine with a modest silicon footprint that en- ables high performance as well as code -

Meshconnect™ EM357 Mini Modules ZICM357SP0, ZICM357SP2 Embertm EM357 Transceiver Based Modules

DATASHEET MeshConnect™ EM357 Mini Modules ZICM357SP0, ZICM357SP2 EmberTM EM357 Transceiver Based Modules Integrated Transceiver Modules for ZigBee / IEEE 802.15.4 Development Kit available: ZICM-EM35X-DEV-KIT-2 DESCRIPTION MeshConnect™ The MeshConnect™ EM357 Mini Modules from EM357 Mini Modules California Eastern Laboratories (CEL) combine high • 192 kB FLASH • 12 kB SRAM performance RF solutions with the market's premier ® ® • 32-bit ARM Cortex™-M3 ZigBee stack. Available in low and high output • Up to 23 GPIO Pins power options (+8dBm and +20dBm), these modules • SPI (Master/Slave), TWI, UART can accommodate variable range and performance • Timers, Serial Wire/JTAG Interface • 5-channel 14-bit ADC requirements. The mini module footprint makes them suitable for a wide range of ZigBee applications. The ZICM357SP0 ZICM357SP2 MeshConnect EM357 Mini Modules are certified and Tx: +8dBm +20dBm qualified, enabling customers to accelerate time to Rx: -100dBm -103dBm Link Budget: +108dB +123dB market by greatly reducing the design and certification phases of development. FEATURES • High RF Performance: • Mini Footprint: CEL's MeshConnect EM357 Mini Modules Up to 123dB RF Link Budget - 0.940" x 0.655" RX Sensitivity: (ZICM357SP0 and ZICM357SP2) are based on the (23.9mm x 16.6mm) -100dBm (ZICM357SP0) Ember EM357 ZigBee compliant SoC radio IC. The • -103dBm (ZICM357SP2) Antenna Options IC is a single-chip solution, compliant with ZigBee 1) Integrated PCB Trace Antenna • Data Rate: 250kbps specifications and IEEE 802.15.4, a complete or • Advanced Cortex-M3 Processor wireless solution for all ZigBee applications. The 2) RF Port for External Antenna • Advanced Power Management • IC consists of an RF transceiver with the baseband Supports Mesh Networks • 16 RF Channels • modem, a hardwired MAC and an embedded 32- AES Encryption • Industry's Premier ZigBee Pro • bit ARM® Cortex™-M3 microcontroller with internal FCC, CE and IC Certifications Stack: EmberZNet PRO™ • RAM (12kB) and Flash (192kB) memory. -

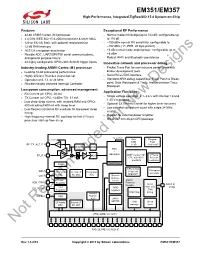

EM351/EM357 High-Performance, Integrated Zigbee/802.15.4 System-On-Chip

EM351/EM357 High-Performance, Integrated ZigBee/802.15.4 System-on-Chip Features Exceptional RF Performance - 32-bit ARM® Cortex -M3 processor - Normal mode link budget up to 103 dB; configurable up - 2.4 GHz IEEE 802.15.4-2003 transceiver & lower MAC to 110 dB - 128 or 192 kB flash, with optional read protection - –100 dBm normal RX sensitivity; configurable to - 12 kB RAM memory –102 dBm (1% PER, 20 byte packet) - AES128 encryption accelerator - +3 dB normal mode output power; configurable up to - Flexible ADC, UART/SPI/TWI serial communications, +8 dBm and general purpose timers - Robust Wi-Fi and Bluetooth coexistence - 24 highly configurable GPIOs with Schmitt trigger inputs Innovative network and processor debug Industry-leading ARM® Cortex -M3 processor - Packet Trace Port for non-intrusive packet trace with - Leading 32-bit processing performance Ember development tools - Highly efficient Thumb-2 instruction set - Serial Wire/JTAG interface - Operation at 6, 12, or 24 MHz - Standard ARM debug capabilities: Flash Patch & Break- - Flexible Nested Vectored Interrupt Controller point; Data Watchpoint & Trace; InstrumentationDesigns Trace Macrocell Low power consumption, advanced management Application Flexibility - RX Current (w/ CPU): 26 mA - Single voltage operation: 2.1–3.6 V with internal 1.8 and - TX Current (w/ CPU, +3 dBm TX): 31 mA 1.25 V regulators - Low deep sleep current, with retained RAM and GPIO: - Optional 32.768 kHz crystal for higher timer accuracy 400 nA without/800 nA with sleep timer - Low external component count -

Efm32lg990 Datasheet

...the world's most energy friendly microcontrollers EFM32LG990 DATASHEET F256/F128/F64 • ARM Cortex-M3 CPU platform • External Bus Interface for up to 4×256 MB of external • High Performance 32-bit processor @ up to 48 MHz memory mapped space • Memory Protection Unit • TFT Controller with Direct Drive • Flexible Energy Management System • Communication interfaces • 20 nA @ 3 V Shutoff Mode • 3× Universal Synchronous/Asynchronous Receiv- • 0.4 µA @ 3 V Shutoff Mode with RTC er/Transmitter • 0.65 µA @ 3 V Stop Mode, including Power-on Reset, Brown-out • UART/SPI/SmartCard (ISO 7816)/IrDA/I2S Detector, RAM and CPU retention • 2× Universal Asynchronous Receiver/Transmitter • 0.95 µA @ 3 V Deep Sleep Mode, including RTC with 32.768 kHz • 2× Low Energy UART oscillator, Power-on Reset, Brown-out Detector, RAM and CPU • Autonomous operation with DMA in Deep Sleep retention Mode • 63 µA/MHz @ 3 V Sleep Mode • 2× I2C Interface with SMBus support • 211 µA/MHz @ 3 V Run Mode, with code executed from flash • Address recognition in Stop Mode • 256/128/64 KB Flash • Universal Serial Bus (USB) with Host & OTG support • 32 KB RAM • Fully USB 2.0 compliant • 86 General Purpose I/O pins • On-chip PHY and embedded 5V to 3.3V regulator • Configurable push-pull, open-drain, pull-up/down, input filter, drive • Ultra low power precision analog peripherals strength • 12-bit 1 Msamples/s Analog to Digital Converter • Configurable peripheral I/O locations • 8 single ended channels/4 differential channels • 16 asynchronous external interrupts • On-chip temperature -

Em358x High-Performance, Integrated Zigbee/802.15.4 System-On-Chip Family

EM358x High-Performance, Integrated ZigBee/802.15.4 System-on-Chip Family Complete System-on-Chip Exceptional RF Performance - 32-bit ARM® Cortex -M3 processor - Normal mode link budget up to 103 dB; configurable up - 2.4 GHz IEEE 802.15.4-2003 transceiver & lower MAC to 110 dB - 256 or 512 kB flash, with optional read protection - –100 dBm normal RX sensitivity; configurable to - 32 or 64 kB RAM memory –102 dBm (1% PER, 20 byte packet) - AES128 encryption accelerator - +3 dB normal mode output power; configurable up to - Flexible ADC, UART/SPI/TWI serial communications, +8 dBm and general purpose timers - Robust Wi-Fi and Bluetooth coexistence Optional USB serial communications - Innovative network and processor debug 24 highly configurable GPIOs with Schmitt trigger inputs - - Packet Trace Port for non-intrusive packet trace with Industry-leading ARM® Cortex -M3 processor Ember development tools - Leading 32-bit processing performance - Serial Wire/JTAG interface - Highly efficient Thumb-2 instruction set - Standard ARM debug capabilities: Flash Patch & Break- - Operation at 6, 12, or 24 MHz point; Data Watchpoint & Trace; InstrumentationDesigns Trace Macrocell - Flexible Nested Vectored Interrupt Controller Application Flexibility Low power consumption, advanced management - Single voltage operation: 2.1–3.6 V with internal 1.8 and - RX Current (w/ CPU): 27 mA 1.25 V regulators - TX Current (w/ CPU, +3 dBm TX): 31 mA - Optional 32.768 kHz crystal for higher timer accuracy - Low deep sleep current, with retained RAM and GPIO: - Low -

Meshconnect™ Em35x Mini Modules Zicm35xsp0 and Zicm35xsp2 Ember TM Em35x Transceiver-Based Modules

MeshConnect™ EM35x Mini Modules ZICM35xSP0 and ZICM35xSP2 Ember TM EM35x Transceiver-Based Modules Integrated Transceiver Modules for ZigBee® / IEEE 802.15.4 Development Kit Available: ZICM-EM35X-DEV-KIT-3 DESCRIPTION MeshConnect™ The MeshConnect™ EM35x Mini Modules from EM35x Mini Modules California Eastern Laboratories (CEL) combine high Powered by Ember® ZigBee® Solutions performance RF solutions with the market's premier KEY FEATURES: EM357 ® • 12kB SRAM ® ™ ZigBee stack. Available in low and high output • 32-bit ARM Cortex -M3 • 192kB Flash power options (+8dBm and +20dBm), these modules • Up to 23 GPIO Pins or can accommodate variable range and performance • SPI (Master/Slave), EM358x requirements. The tiny module footprint makes them TWI and UART • Up to 64kB SRAM suitable for a wide range of ZigBee applications. The • Timers and Serial • Up to 512kB Flash (Supports OTA) Wire/JTAG Interface MeshConnect EM35x Mini Modules are certified and • Optional USB qualified, enabling customers to accelerate time to • 5-Channel 14-bit ADC Controller market by greatly reducing the design and certification ZICM35xSP0 ZICM35xSP2 phases of development. Tx: +8dBm +20dBm Rx: -100dBm -103dBm CEL’s MeshConnect EM35x Mini Modules Link Budget: +108dB +123dB (ZICM35xSP0 and ZICM35xSP2) are based on the Ember EM35x (EM357 and EM358x) ZigBee ADDITIONAL FEATURES • • compliant System on Chip (SoC) radio ICs. Each IC is Data Rate: 250kbps Antenna Options: • Advanced Power Management 1) Integrated PCB Trace Antenna a complete single-chip solution, compliant -

Silicon Labs Expands Wireless Portfolio to Include Ember® Zigbee® Solutions for the "Internet of Things"

November 5, 2012 Silicon Labs Expands Wireless Portfolio to Include Ember® ZigBee® Solutions for the "Internet of Things" EM35x System-on-Chip and Network Co-Processor Products Now Available Through Silicon Labs' Global Distribution Channel AUSTIN, Texas--(BUSINESS WIRE)-- Silicon Laboratories Inc. (Nasdaq: SLAB), a leader in high-performance, analog-intensive, mixed-signal ICs, today announced the addition of Ember® ZigBee® solutions to its portfolio of low-power wireless embedded devices for the Internet of Things (IoT). Available now through Silicon Labs' global distribution channel, the EM35x system-on- chip (SoC) and network co-processor (NCP) products and EmberZNet PRO software enable designers to develop high- performance, low-power and reliable 2.4 GHz wireless mesh networking solutions for smart energy, home automation, security, lighting, and other monitoring and control applications for the rapidly growing IoT market. Industry experts predict that the number of connected devices for the IoT will surpass 15 billion nodes by 2015 and reach 50 billion nodes by 2020. By adding Ember ZigBee solutions to its portfolio of sub-GHz wireless ICs, wireless microcontrollers (MCUs), and 8- and 32-bit mixed-signal MCUs, Silicon Labs is uniquely positioned to provide the wireless connectivity and low- power processing platforms for many of the connected devices that enable the IoT. The Ember ZigBee platform is the most integrated, comprehensive and feature-rich ZigBee solution available for 2.4 GHz wireless networks, delivering unmatched wireless performance, low power consumption and code density in a compact package. The most widely used ZigBee platform for mesh networking applications, EM35x devices can be deployed as SoCs for cost-sensitive, low-power sensor networks and other simple connected devices or configured as NCPs for complex applications running on high-performance applications processors.