SX/E Programmer Manual

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Embedded Systems Building and Programming Embedded Devices

Embedded Systems Building and Programming Embedded Devices PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Tue, 29 May 2012 01:04:04 UTC Contents Articles Wikibooks:Collections Preface 1 Embedded Systems/Embedded Systems Introduction 3 Embedded Systems/Terminology 7 Microprocessor Basics 10 Embedded Systems/Microprocessor Introduction 10 Embedded Systems/Embedded System Basics 11 Embedded Systems/Microprocessor Architectures 13 Embedded Systems/Programmable Controllers 16 Embedded Systems/Floating Point Unit 18 Embedded Systems/Parity 20 Embedded Systems/Memory 21 Embedded Systems/Memory Units 24 Programming Embedded Systems 25 Embedded Systems/C Programming 25 Embedded Systems/Assembly Language 31 Embedded Systems/Mixed C and Assembly Programming 34 Embedded Systems/IO Programming 42 Embedded Systems/Serial and Parallel IO 43 Embedded Systems/Super Loop Architecture 44 Embedded Systems/Protected Mode and Real Mode 46 Embedded Systems/Bootloaders and Bootsectors 47 Embedded Systems/Terminate and Stay Resident 48 Real Time Operating Systems 49 Embedded Systems/Real-Time Operating Systems 49 Embedded Systems/Threading and Synchronization 51 Embedded Systems/Interrupts 54 Embedded Systems/RTOS Implementation 55 Embedded Systems/Locks and Critical Sections 57 Embedded Systems/Common RTOS 60 Embedded Systems/Common RTOS/Palm OS 63 Embedded Systems/Common RTOS/Windows CE 64 Embedded Systems/Common RTOS/DOS 64 Embedded Systems/Linux 65 Interfacing 68 Embedded Systems/Interfacing -

COOLANT OIL CONTROL SYSTEM in VMC MACHINE ”Is the Bonafide Work Of

COOLANT OIL CONTROL SYSTEM IN VMC MACHINE A PROJECT REPORT Submitted by RAJAGANAPATHY.S (13BEI111) GOWTHAMVEL.P (13BEI018) SANTHOSE PRABU.R (13BEI050) in partial fulfillment for the award of the degree of BACHELOR OF ENGINEERING in ELECTRONICS AND INSTRUMENTATION ENGINEERING KUMARAGURU COLLEGE OF TECHNOLOGY (An Autonomous Institution, Affiliated to Anna University,Chennai) COIMBATORE 641049 APRIL 2017 1 COOLANT OIL CONTROL SYSTEM IN VMC MACHINE A PROJECT REPORT Submitted by RAJAGANAPATHY.S (13BEI111) GOWTHAMVEL.P (13BEI018) SANTHOSE PRABU.R (13BEI050) in partial fulfillment for the award of the degree of BACHELOR OF ENGINEERING in ELECTRONICS AND INSTRUMENTATION ENGINEERING KUMARAGURU COLLEGE OF TECHNOLOGY (An Autonomous Institution, Affiliated to Anna University,Chennai) COIMBATORE 641049 APRIL 2017 2 BONAFIDE CERTIFICATE Certified that this project report “COOLANT OIL CONTROL SYSTEM IN VMC MACHINE ”is the bonafide work of RAJAGANAPATHY.S (13BEI111) GOWTHAMVEL.P (13BEI018) SANTHOSE PRABU.R (13BEI050) who carried out the project work under my supervision. SIGNATURE SIGNATURE Dr.N.EZHILARASI Mr.S.SARAVANA KUMAR HEAD OF THE DEPARTMENT SUPERVISOR Dept. of Electronics and Instrumentation Assistant Professor Kumaraguru College of Technology Dept. of Electronics and Instrumentation Coimbatore-641049 Kumaraguru College of Technology Coimbatore-641049 The candidates were examined by us in the project viva voce examination held on INTERNAL EXAMINER EXTERNAL EXAMINER 3 ACKNOWLDEGEMENT The satisfaction that accompanies the successful completion of any task would be incomplete without mentioning about the people whose constant guidance and encouragement crowns all effort with success. We are greatly indebted to our beloved Principal Dr.R.S.KUMAR, who has been the backbone of all our deeds. We express our gratitude to Dr.N.EZHILARASI, Head, Department of Electronics and Instrumentation Engineering, Kumaraguru College of Technology for her constant encouragement. -

Con Smart Card

SPECIALE PARALLAX SX Microcontrollori 8 bit ad alta velocità DISPOSITIVO MULTIFUNZIONE CON SMART CARD • Chiave Elettronica • Credito a scalare FEBBRAIO n° 260 • Anno 23 • Attivazione utenza www.farelettronica.com PLC PER TUTTI Al via il nuovo corso che vi guiderà passo-passo alla programmazione dei PLC utilizzando LADDER e BASIC RUBRICA MHZ L’adattamento d’impedenza in radiofrequenza PIC-SUDOKU - Milano il CPM di Roserio tassa presso la relativa che si impegna a pagare all'editore restituire recapito, mancato Il sorgente in MikroBasic per risolvere La divisione di codice nelle trasmissioni digitali una qualsiasi griglia Sudoku IDEE DI PROGETTO , DCB Milano. In caso di PIC & MikroC RS232 Quadruplicatore di tensione con TD310 Come leggere valori analogici Tutto quello Beep Beep digitale utilizzando che c’è da sapere sull’interfaccia DS8669 2-digit bcd to 7-segment decoder/driver il convertitore seriale per eccellenza Sensore di precisione di temperatura fahrenheit AD del PIC con LM34 Alimentatore phantom Convertitore frequenza/tensione con LM2907 per microfoni Barra diodi led con LM3916 Collegare microfoni www.farelettronica.com Duplicatore di tensione professionali ad un mixer tradizionale? € 5,50 Con questo alimentatore si può! Onda quadra e triangolare con LM566C MENSILE Poste Italiane Spa - Spedizione in abbonamento Postale - D.L. 353/2003 (conv. In L. 27/02/2004 n. 46) art. 1, comma1 In L. 27/02/2004 (conv. 353/2003 - D.L. Postale Italiane Spa - Spedizione in abbonamento MENSILE Poste ININ EDICOLA EDICOLA NonNon perdereperdere ilil numeronumero didi questoquesto mesemese servizioservizio MIPMIP M ore I nfo P lease! www.farelettronica.com Richiedi maggiori informazioni sui contenuti di Fare Elettronica, visita il sito: www.farelettronica.com/mip Oppure compila questo modulo ed invialo via fax al numero 02 66508225 Numero della rivista 260 Codici MIP* (da compilare) DATI DEL LETTORE Nome Cognome Azienda Indirizzo Azienda Cap Città Prov. -

Embedded Solutions

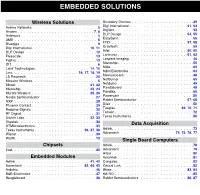

EMBEDDED SOLUTIONS Wireless Solutions Boundary Devices . .49 Ackme Networks . 5 Digi International . 51, 52 Anaren . 7, 8 Digilent . .53 Antenova . 5 DLP Design . 54, 55 AMS . .6 EasySync. .56 Bluegiga . 9 FTDI . 57, 58 Digi International . 10, 11 Gravitech . .59 DLP Design . .12 Intel. 50, 60 Freescale. .13 Lantronix . 61, 62 Fujitsu . .13 Leopard Imaging . .48 IDT . 6 Microchip . .50 Laird Technologies . 14, 15 Mide . 63 Linx. 16, 17, 18, 19 MikroElektronika . 64 LS Research . .20 Minnowboard. .48 Maestro Wireless. 6 NetBurner . 65 Micrel. 21, 22 Netduino . 49 Microchip . 23, 24 Pandaboard . .48 Murata Wireless . 25, 26 Parallax. .66 Nordic Semiconductor . 27 Powercast . 50 NXP . 28 Rabbit Semiconductor . 67, 68 Phoenix Contact . 29 Silex . 50 Redpine Signals . 30 Taoglas. 69, 70, 71 RF Digital. .31 Terasic . .72 Silicon Labs . 32, 33 Texas Instruments . .50 Skyetek. .34 STMicroelectronics. .35 Data Acquisition Texas Instruments . 36, 37, 38 Adlink. .73 Wiznet . .39 Advantech . 74, 75, 76, 77 Wurth. .13 Single Board Computers Chipsets Adlink. .78 Intel. .40 Advantech . 79 Arbor . 80 Embedded Modules Axiomtek . 81 Adlink. 41, 42 Congatec . .82 Advantech . 43, 44, 45 Critical Link. .82 Arduino . .46 iBase . 83, 84 B&B Electronics . 47 KA-RO . .85 Beagleboard . .48 Rabbit Semiconductors . 86, 87 WiFi Modules and Chip Antennas Wireless Solutions WALLABY WICED WI-FI NETWORKING MODULES ACKme Networks AMW004 Wallaby WICED Wi-Fi Networking Module is a fully certified small form factor, low power WICED-based Wi-Fi networking module perfectly suited to deeply embedded applications for medium to high volumes. The module runs an embedded TCP/IP networking stack with SSL/TLS/HTTPS security and includes an onboard PCB trace antenna and u.FL connector all in a physical footprint of just 31.2mm x 17.8mm (1.25" x 0.7"). -

Nuts and Volts

Archivo Descargado desde las WEBS http://www.enigmaelectronica.tk Http://www.enigma.phpnet.us By enigmaelectronica > 01 $7.00 CANADA $5.50 74470 89295 03 U.S. Cover.qxd 12/11/2008 1:25 PM Page 1 Vol. 30 No. 1 NUTS & VOLTS PROTO BUDDY • SPICE SIMULATION • MOSFETS • How To - SMT SOLDERING January 2009 Jan 09.qxd 12/10/2008 6:02 PM Page 6 January 2009 www.nutsvolts.com C o n t e n t s Features 50 Power MOSFETs ■ By Gerard Fonte Part 1 will cover the theory behind these useful devices that have a lot of overlooked features. 54 A Touch of Spice ■ By Peter Stonard This month, make discoveries about IC circuits that are well-known and learn more about the concepts of sub-circuits and macromodels. 60 How To: Surface Mount Soldering ■ By Robert Doerr Get over your fear of working with these tiny components. Page 44 Page 40 Projects Columns 34 Instrumentation for Model Rocketry Incorporate additional instrumentation to a flight recorder 12 TechKnowledgey 2009 to measure a rocket’s rate of roll, relative altitude, and Events, Advances, and News booster-stage separation detection. ■ By Michael Bessant Topics covered include reconnecting brain ●●●● Advanced Level cells, a new unified storage appliance, don’t mix headphones and pacemakers, plus more. 40 16x16 Tri-Colored LED Matrix — 15 Personal Robotics Real Time Clock for the Parallax SX52 Understanding, Designing & Constructing This project allows the user to create their own scrolling Robots display to show the time (or other messages) in multiple Robo resolutions for 2009. colors. -

INDUSTRIAL CONTROL Control Via the Internet

E MBEDDED PC CIRCUIT MONTHLY SECTION CELLARINK® T H E C O M P U T E R A P P L I C A T I O N S J O U R N A L # 1 0 0 N O V E M B E R 1 9 9 8 INDUSTRIAL CONTROL Control via the Internet Making Buildings Smarter Embedded Linux Toughen up that PC BIOS $3.95 U.S. $4.95 Canada TASK MANAGER Netting 100 ® th INK n your hands you hold the 100 issue of i Circuit Cellar INK. Have you been here from the beginning, over 10 years ago? Or, maybe you just T H E C O M P U T E R A P P L I C A T I O N S J O U R N A L picked up this issue from the newsstand today for the EDITORIAL DIRECTOR/PUBLISHER ASSOCIATE PUBLISHER very first time. No matter. It’s definitely a time for celebration! Steve Ciarcia Sue Skolnick I find it fitting that a milestone issue like this one has the theme MANAGING EDITOR CIRCULATION MANAGER Industrial Control. After all, home automation and building control has been Elizabeth Laurençot Rose Mansella a Circuit Cellar hallmark from the start. It’s nice to see that although the TECHNICAL EDITORS CHIEF FINANCIAL OFFICER Michael Palumbo Jeannette Ciarcia implements have of course changed over the years, the interests haven’t. Rob Walker ART DIRECTOR INK still focuses on what the readers want. WEST COAST EDITOR KC Zienka But , the implements have changed indeed. -

Embedded Systems Building and Programming Embedded Devices

Embedded Systems Building and Programming Embedded Devices PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Wed, 05 Oct 2011 11:42:21 UTC Contents Articles Wikibooks:Collections Preface 1 Embedded Systems/Embedded Systems Introduction 2 Embedded Systems/Terminology 6 Microprocessor Basics 9 Embedded Systems/Microprocessor Introduction 9 Embedded Systems/Embedded System Basics 10 Embedded Systems/Microprocessor Architectures 12 Embedded Systems/Programmable Controllers 15 Embedded Systems/Floating Point Unit 17 Embedded Systems/Parity 19 Embedded Systems/Memory 20 Embedded Systems/Memory Units 23 Programming Embedded Systems 24 Embedded Systems/C Programming 24 Embedded Systems/Assembly Language 30 Embedded Systems/Mixed C and Assembly Programming 32 Embedded Systems/IO Programming 40 Embedded Systems/Serial and Parallel IO 41 Embedded Systems/Super Loop Architecture 42 Embedded Systems/Protected Mode and Real Mode 44 Embedded Systems/Bootloaders and Bootsectors 45 Embedded Systems/Terminate and Stay Resident 46 Real Time Operating Systems 47 Embedded Systems/Real-Time Operating Systems 47 Embedded Systems/Threading and Synchronization 49 Embedded Systems/Interrupts 52 Embedded Systems/RTOS Implementation 53 Embedded Systems/Locks and Critical Sections 55 Embedded Systems/Common RTOS 58 Embedded Systems/Common RTOS/Palm OS 60 Embedded Systems/Common RTOS/Windows CE 61 Embedded Systems/Common RTOS/DOS 61 Embedded Systems/Linux 62 Interfacing 65 Embedded Systems/Interfacing -

Nuts and Volts

WWW.GiURUMELE.Hi2.RO WWW.RADiOSCAMATORUL.Hi2.RO > 01 $7.00 CANADA $5.50 74470 89295 03 U.S. Cover.qxd 12/11/2008 1:25 PM Page 1 Vol. 30 No. 1 NUTS & VOLTS PROTO BUDDY • SPICE SIMULATION • MOSFETS • How To - SMT SOLDERING January 2009 Full Page.qxd 12/4/2007 4:26 PM Page 2 WWW.GiURUMELE.Hi2.RO WWW.RADiOSCAMATORUL.Hi2.RO Full Page.qxd 12/10/2008 5:27 PM Page 3 WWW.GiURUMELE.Hi2.RO WWW.RADiOSCAMATORUL.Hi2.RO Wi-Fi and Ethernet Versions Full Page.qxd 11/5/2008 4:57 PM Page 4 WWW.GiURUMELE.Hi2.RO WWW.RADiOSCAMATORUL.Hi2.RO Full Page.qxd 12/10/2008 5:29 PM Page 5 WWW.GiURUMELE.Hi2.RO WWW.RADiOSCAMATORUL.Hi2.RO Experience a Faster Way to Search for Components! Jameco Electronics’ new catalog and enhanced to quickly jump from catalog to website to view Jameco.com website are two tools that are designed additional specifications, application notes, photos to work together to give electronic professionals and more products. You'll find exactly what you're faster access to the hottest components in looking for without having to wade through hundreds the industry. of thousands of products on a complicated website Color coded references throughout the catalog or wielding a twenty pound catalog. assist you in analyzing a wide range of brand With a flip of the page or a click of the mouse, choices (from franchise sourced to house brands to you have all the tools you need at your fingertips. factory overruns) offering you more pricing options Reach for Jameco first and order your than you'll see anywhere else. -

An Introduction to Arduino an Introduction to Arduino PDF GUIDE

An Introduction to Arduino An Introduction to Arduino PDF GUIDE: http://antoinettejcitizen.com/files/AICCM_Arduino.pdf Michelle Woulahan Antoinette J. Citizen Creative media facilitator at City of Melbounre Electronic media artist Events listing: http://bit.do/techEvents Website: antoinettejcitizen.com Microcontrollers A microcontroller is a very small computer on a single integrated circuit (IC). All computers have several things in common: • CPU (central processing unit) that executes programs. • RAM (random-access memory) where it can store variables. • Input and output devices for interaction. Desktop computers are “general purpose computers” that can run any of thousands of programs. Microcontrollers are “special purpose computers.” Microcontrollers do one thing well. Microcontrollers are often embedded onto a single printed circuit board. This board provides all of the circuitry necessary for a useful control task. The intention is that the board is immediately useful to an application developer, without them needing to spend time and effort in developing the controller hardware. BASIC Stamp Microcontroller: • Microchip Technology PIC • Parallax SX processor. mbed Microcontroller: • ARM Cortex IOIO OTG Microcontroller: • Microchip Technology PIC Arduino Microcontroller: Atmel AVR microcontroller • ATmega8 • ATmega168 • ATmega328 • ATmega1280 • ATmega2560 Arduino Single board microcontrollers like the Arduino are able to read inputs - light on a sensor, a finger on a button, or a Twitter message - and turn it into an output - activating a motor, turning on an LED, publishing something online. Arduino is an open-source prototyping platform based on easy-to-use hardware and software. Examples: http://www.creativeapplications.net/category/arduino-2/ There are lots of different types of Arduino boards. UNO is currently the most common and easily the best documented and best supported of the Arduinos. -

Nuts and Volts

WWW.GiURUMELE.Hi2.RO WWW.RADiOSCAMATORUL.Hi2.RO Cover.qxd 6/4/2008 5:56 PM Page 1 Vol. 29 No. 7 NUTS & VOLTS ILLUMINAME • POWER SUPPLY • DEFCON BADGE • WEBSTER 08 Full Page.qxd 12/4/2007 4:26 PM Page 2 WWW.GiURUMELE.Hi2.RO WWW.RADiOSCAMATORUL.Hi2.RO Full Page.qxd 6/2/2008 11:31 AM Page 3 WWW.GiURUMELE.Hi2.RO WWW.RADiOSCAMATORUL.Hi2.RO Free Book with Kit Full Page.qxd 6/3/2008 10:57 AM Page 4 WWW.GiURUMELE.Hi2.RO WWW.RADiOSCAMATORUL.Hi2.RO Full Page.qxd 3/5/2008 12:22 PM Page 5 SERIAL TO ETHERNET SOLUTIONS Simple Ethernet connectivity for serial devices Works out of the box - no programming is required Device P/N: SB70-100CR Customize to suit any Kit P/N: NNDK-SB70-KIT application with low-cost $69 SB70 WWW.GiURUMELE.Hi2.ROdevelopment kit 2-port serial-to-Ethernet server Features: Qty. 100 WWW.RADiOSCAMATORUL.Hi2.ROwith TTL support 10/100 Ethernet TCP/UDP mode DHCP/Static IP Support Data rates up to 921.6kbps Web-based configuration Need a custom solution? NetBurner Serial to Ethernet Development Kits are available Device P/N: SB72-EX-100CR to customize any aspect of Kit P/N: NNDK-SB72EX-KIT operation including web pages, data filtering, or custom network SB72EX $139 applications. All kits include 2-port serial-to-Ethernet server platform hardware, ANSI C/C++ Qty. 100 with RS-232 & RS-485/422 support compiler, TCP/IP stack, web server, e-mail protocols, RTOS, flash file system, Eclipse IDE, debugger, cables and power supply.