Demand-Side Load Management Using Single-Phase Residential Static VAR Compensators

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Static Var Compensator (SVC)

Electricity and New Energy Static Var Compensator (SVC) Courseware Sample 86370-F0 Order no.: 86370-10 First Edition Revision level: 01/2015 By the staff of Festo Didactic © Festo Didactic Ltée/Ltd, Quebec, Canada 2012 Internet: www.festo-didactic.com e-mail: [email protected] Printed in Canada All rights reserved ISBN 978-2-89640-540-4 (Printed version) Legal Deposit – Bibliothèque et Archives nationales du Québec, 2012 Legal Deposit – Library and Archives Canada, 2012 The purchaser shall receive a single right of use which is non-exclusive, non-time-limited and limited geographically to use at the purchaser's site/location as follows. The purchaser shall be entitled to use the work to train his/her staff at the purchaser's site/location and shall also be entitled to use parts of the copyright material as the basis for the production of his/her own training documentation for the training of his/her staff at the purchaser's site/location with acknowledgement of source and to make copies for this purpose. In the case of schools/technical colleges, training centers, and universities, the right of use shall also include use by school and college students and trainees at the purchaser's site/location for teaching purposes. The right of use shall in all cases exclude the right to publish the copyright material or to make this available for use on intranet, Internet and LMS platforms and databases such as Moodle, which allow access by a wide variety of users, including those outside of the purchaser's site/location. -

Static Var Compensator Device

Static Var Compensator device 1 2 3x 1x SVC_1 Static Var Compensator device ..................................................................................... 1 1 Description ..................................................................................................................... 1 2 Parameters..................................................................................................................... 3 2.1 User defined Initial values .................................................................................... 3 2.2 Scopes..................................................................................................................... 5 3 References..................................................................................................................... 6 1 Description The Static Var Compensator (SVC) is a shunt device of the Flexible AC Transmission Systems (FACTS) family using power electronics to control power flow and improve transient stability on power grids [1]. In general, the SVC can be used where continuous and fast control or reactive power is required to meet any or all of the following objectives [2]: • Improved voltage regulation; • Enhancement of steady state and dynamic stability; • Reduction of over voltages; • Reduction of voltage flicker; • Damping of sub synchronous oscillations; • Reduction of voltage or current unbalances. This SVC is a generic model using three Thyristor Switched Capacitor banks (TSC) and one Thyristor Controlled Reactor (TCR). The SVC regulates voltage -

The Design and Performance of Static Var Compensators for Particle Accelerators

CERN-ACC-2015-0104 [email protected] The design and performance of Static Var Compensators for particle accelerators Karsten Kahle, Francisco R. Blánquez, Charles-Mathieu Genton CERN, Geneva, Switzerland, Keywords: «Static Var Compensator (SVC)», «reactive power compensation», «power quality», «particle accelerator», «harmonic filtering». Abstract Particle accelerators, and in particular synchrotrons, represent large cycling non-linear loads connected to the electrical distribution network. This paper discusses the typical design and performance of Static Var Compensators (SVCs) to obtain the excellent power quality levels required for particle accelerator operation. Presented at: EPE 2015, 7-10 September 2015, Geneva, Switzerland Geneva, Switzerland October, 2015 CERN-ACC-2015-0104 05/10/2015 The design and performance of Static Var Compensators for particle accelerators Karsten Kahle, Francisco R. Blánquez, Charles-Mathieu Genton CERN – European Organization for Nuclear Research 1211 Geneva 23, Switzerland [email protected], [email protected], [email protected] Keywords «Static Var Compensator (SVC)», «reactive power compensation», «power quality», «particle accelerator», «harmonic filtering». Abstract Particle accelerators, and in particular synchrotrons, represent large cycling non-linear loads connected to the electrical distribution network. This paper discusses the typical design and performance of Static Var Compensators (SVCs) to obtain the excellent power quality levels required for particle accelerator operation. 1. Introduction For the electrical distribution network, particle accelerators represent large cycling non-linear electric loads with a variable power factor. The twelve-pulse thyristor power converters for the main dipole and quadrupole magnets represent the major part of the load. The large amplitudes, and the steep gradients of the power cycles require rapid reactive power control, for voltage stabilisation and compensation of varying reactive power. -

Static Var Compensator Solutions

GE Grid Solutions Static Var Compensator Solutions imagination at work Today’s Environment GE’s Solution Todays transmission grid is changing and becoming more complex to GE’s Static Var Compensator (SVC) solution allows grid operators to gain manage. Utilities globally are experiencing challenges such as: accurate control of reactive network power, increase power transfer • Increase in global demand for electricity capability and improve steady-state and dynamic stability of the grid. • Thermal plant retirements coupled with an increase in renewable SVC controls transmission line voltage to compensate for reactive power generation, often remote from load centers balance by absorbing inductive reactive power when voltage is too high and • Stringent requirements by regulatory authorities on power quality generating capacitive reactive power when voltage is too low. • Interconnected grids Compared to the investment required for additional transmission • Aging transmission infrastructure networks, SVC provides customers with a flexible solution that has minimal These challenges can make power flow stability more complex for network infrastructure investment, low environmental impact, rapid implementation operators as they manage stability issues under fault clearing and post-fault time and improved return on investment. conditions. Leveraging Design Best Practices with the GE Store The increase in demand and renewables combined with aging infrastructure can cause voltage on the grid to fluctuate, including harmonics, flicker GE’s power electronics -

Coordinated Excitation and Static Var Compensator Control with Delayed Feedback Measurements in SGIB Power Systems

energies Article Coordinated Excitation and Static Var Compensator Control with Delayed Feedback Measurements in SGIB Power Systems Haris E. Psillakis 1 and Antonio T. Alexandridis 2,* 1 School of Electrical and Computer Engineering, National Technical University of Athens, 15780 Athens, Greece; [email protected] 2 Department of Electrical and Computer Engineering, University of Patras, 26504 Patras, Greece * Correspondence: [email protected]; Tel.: +30-261-099-6404 Received: 25 March 2020; Accepted: 22 April 2020; Published: 1 May 2020 Abstract: In this paper, we present a nonlinear coordinated excitation and static var compensator (SVC) control for regulating the output voltage and improving the transient stability of a synchronous generator infinite bus (SGIB) power system. In the first stage, advanced nonlinear methods are applied to regulate the SVC susceptance in a manner that can potentially improve the overall transient performance and stability. However, as distant from the generator measurements are needed, time delays are expected in the control loop. This fact substantially complicates the whole design. Therefore, a novel design is proposed that uses backstepping methodologies and feedback linearization techniques suitably modified to take into account the delayed measurement feedback laws in order to implement both the excitation voltage and the SVC compensator input. A detailed and rigorous Lyapunov stability analysis reveals that if the time delays do not exceed some specific limits, then all closed-loop signals remain bounded and the frequency deviations are effectively regulated to approach zero. Applying this control scheme, output voltage changes occur after the large power angle deviations have been eliminated. The scheme is thus completed, in a second stage, by a soft-switching mechanism employed on a classical proportional integral (PI) PI voltage controller acting on the excitation loop when the frequency deviations tend to zero in order to smoothly recover the output voltage level at its nominal value. -

Static Var Compensator (SVC) Course 86370

Static Var Compensator (SVC) Course 86370 The Static Var Compensator (SVC) course explores the operation of the SVC (i.e., thyristor- controlled reactor, thyristor-switched capacitors, and SVC controller), as well as the automatic control of the voltage or the power factor in three-phase power networks. As part of the FACTS (Flexible AC Transmission Systems), the SVC technology is used by power utilities to maintain voltage quality for the distribution system as well as by industrial plants for dynamic power factor correction at their electric power entrance. Topic Coverage: for dynamic power factor correction in arc furnace » Examine the main components of a static var applications and other industrial applications. compensator (SVC). » Bonus content: using the equipment in this course, » Understand the simplifi ed diagram of an SVC. the Three-Phase AC Power Circuits and Three-Phase Transformer Banks courses can also be completed. » Analyze the three main components of an SVC: − The thyristor-controlled reactor (TCR) Features and Benefi ts: − The thyristor-switched capacitor (TSC) » Real operating static var compensator (TCR-TSC type). − The fi xed capacitor (FC) » Includes the SCADA view window of » Analyze the operation principles of SVCs when used an SVC. for voltage compensation of ac transmission lines. » Study and experiment with voltage and » Explore the reasons behind power factor correction in reactive power control. industrial applications that absorb large amounts of reactive power from the ac power network. SMART 0 INSTRUMENTATION -

Comparison of Different Types of Compensating Devices in Power System

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395 -0056 Volume: 03 Issue: 11 | Nov -2016 www.irjet.net p-ISSN: 2395-0072 Comparison of Different types of Compensating Devices in Power System Arun Pundir1, Gagan Deep Yadav2 1Mtech Scholar, YIET Gadhauli, India 2Assistant Professor, YIET, Gadhauli, India ---------------------------------------------------------------------***--------------------------------------------------------------------- Abstract - The quality of electrical power in a network is WECS is one of the most attractive options among all the RES a major concern which has to be examined with caution in Reactive power compensation is an effective technique to order to achieve a reliable electrical power system network. enhance the electric power network, there is need for Reactive power compensation is a means for realizing the goal regulated reactive power compensation which can be done of a qualitative and reliable electrical power system. This either with synchronous condensers, Static VAR paper made a comparative review of reactive power Compensators (SVCs) or Static Synchronous Compensators compensation technologies; the devices reviewed include (STATCOM) [1], [4], [5]. Synchronous Condenser, Static VAR Compensator (SVC) and There are different technologies for reactive power Static Synchronous Compensator (STATCOM). These compensation, these includes; Capacitor Bank, Series technologies were defined, critically examined and compared, Compensator, Shunt Reactor, Static VAR Compensator (SVC), -

Protection of Static VAR Compensator Summary Keywords 1. Introduction

Study Committee B5 Colloquium October 19-24, 2009 204 Jeju Island, Korea Protection of Static VAR Compensator Halonen, Mikael*. Thorvaldsson, Björn. Wikström, Kent. ABB AB, FACTS Sweden Summary Static Var Compensator (SVC) protection is presented. SVC systems come in a wide number of arrangements, and are custom designed for specific applications. For SVC applications the control and protection system plays an essential role in the overall performance of the power system. From protection standpoint, an extensive protection system is generally required for SVCs to optimise the equipment operational limits for maximum utilisation. This paper outlines the experience gained from, and design aspects of relay protection for SVC’s. The paper analyzes different fault cases and describes different relay protection principles applicable to SVCs. It also includes an overview of SVC protection methods. It covers the protection of the connection of the SVC to the substation busbars. For the SVC itself the power transformer, the SVC medium voltage busbar and the active branches, i.e. TCR, TSC and harmonic filters are of specific interest. These branches are exposed to severe current and voltage transient during system disturbances. Insensitivity to harmonics and DC current are essential. SVCs are normally ungrounded on the MV bus and residual voltage protection is used to detect ground faults. If selective earth fault protection is required for the SVC, this can be accomplished by using either a grounding transformer or an automatic reclosure scheme. Special protection functions are integrated in the SVC control system to detect abnormal operating conditions and to react rapidly to avoid damage and unnecessary tripping by the plant protection system. -

POWER FACTOR IMPROVEMENT USING OPEN LOOP FEEDBACK STATIC VAR COMPENSATOR (SVC) Vasudeva Naidu1, Bindu Priya2, Shruti Chauhan3, Tabrez Khan4, A.M Thukaram5

POWER FACTOR IMPROVEMENT USING OPEN LOOP FEEDBACK STATIC VAR COMPENSATOR (SVC) Vasudeva Naidu1, Bindu Priya2, Shruti Chauhan3, Tabrez Khan4, A.M Thukaram5 1,2 Asst.Professor, GITAM University, E.E.E Department, Hyderabad, (India) 3,4, 5 Students, GITAM University, E.E.E Department, Hyderabad, (India) ABSTRACT This paper mainly design the single phase open feedback loop SVC and improve power factor of the power system using single phase loads are induction motors, arc lamps etc. These are inductive in nature and hence have low lagging power factor. The low power factor is highly undesirable as it causes an increase in current, resulting in additional losses of active power in all the elements of power system from power system down to the utilisation devices. To compensate reactive power and improve the power factor by using a static VAR compensator, it consisting converter (2-level SCR) with capacitor bank. This work deals with the performance evaluation through analytical studies and practical implementation on an existing system consisting of a distribution transformer of 1phase, 50Hz, 230V/12V capacity. The PIC controller determines firing pulse of IGBT to compensate excessive reactive power component for PF improvement Keywords: Capacitor bank, Microcontroller, Power factor, Reactive power, Static VAR compensator. I. INTRODUCTION We know that power loss is taking place in our low voltage distribution systems on account of poor power factor, due to limited reactive power compensation facilities and their improper control. In rural power distribution systems in wide spread remote areas, giving rise to more inductive loads resulting in very low power factors. It is necessary to closely match reactive power with the load so as to improve power factor and reduce the losses. -

Static Var Compensators Protection Scheme Study

STATIC VAR COMPENSATORS PROTECTION SCHEME STUDY CASE STUDY: MAHADIYA SUBSTATION SVC By MOHAMMED ESSAM ELDIEN MOHAMMED ELAHAJ IBRAHEM INDEX NO 124082 Supervisor Dr. Elfadil Zakaria Yahia A REPORT SUBMITTED TO University of Khartoum In partial fulfillment for the degree of B.Sc. (HONS) Electrical and Electronics Engineering (POWER ENGINEERING) Faculty of Engineering Department of Electrical and Electronics Engineering October 2017 DECLARATION OF ORGINALITY I declare this report entitled “Static VAR compensators protection scheme study” is our own work except as cited in references. The report has been not accepted for any degree and it is not being submitted currently in candidature for any degree or other reward. Signature: ____________________ Name: _______________________ Date: _______________________ ii ACKNOWLEDGEMENT First, all praise and thanks to Allah for providing me with this opportunity and granting me the capability to proceed successfully. To my mother, who brought to life and raised me to be the man that I am today. To my father who taught me the patience and self-confidence. I would like to express my very great appreciation to Dr. Elfadil Zakaria Yahia my supervisor for his valuable and constructive suggestions during the planning and development of this project Many thanks to my seniors ENG Azza Gasim alsaid for the great guidance and effort. Special thanks to my project partner for his hard work, support and cooperation. iii Abstract In this project the protection scheme of the static VAR compensators of the MAHADYIA substation has been studied. Power system stability is very important, so SVC plays a major role in voltage regulation and improving the stability of the system due to its fast response and high capability. -

Static Var Compensator

STATIC VAR COMPENSATOR Effective and reliable power quality solution for MERUS – SVC heavy industries and electrical utilities. FUNCTIONS OF TAILORED Are you searching for a solution to THE MERUS improve the productivity, capacity STATIC VAR COMPENSATOR: and reliability of your plant? Voltage POWER • Voltage stabilization instability, flicker and harmonic and load balancing by distortions are commonly experienced injecting inductive or QUALITY power quality challenges. Poor power capacitive reactive power quality can undermine the productivity, • Flicker mitigation capacity and reliability of industrial through dynamic response to fast SOLUTION plants with challenging loads such as uctuation of loads TO SUIT YOUR NEEDS electric arc furnaces. Power quality • Maintaining of power problems also impact the stability and factor to desired levels transmission capacity of the supply • Harmonic mitigation network. • Improved voltage on loadbus GOOD POWER QUALITY SAVES MONEY AND ENERGY Merus Power Static Var Compensator is an effective and reliable power quality solution – an investment that pays off quickly. Fast and effective response to voltage variations, flicker and harmonic distortions bring proven benefits to both heavy industrial plants and supply network. Merus SVC releases the undermined capacity while improving productivity and reliability in your plant at the same time. Supply network and neighboring facilities enjoy greater voltage stabilization and enhanced transmission capacity. Each SVC system is tailor-made to fit the network fault level and load parameters. Voltage 1,02 WITH SVC 1,00 0,98 WITHOUT SVC 0,96 0,94 0,92 One division/second 0,90 0 1 2 3 4 5 6 7 8 9 10 Seconds CUSTOMER APPLICATION CUSTOMIZED SOLUTION FOR BENEFITS: CHALLENGING APPLICATIONS • Increased plant Merus Static Var Compensator is an productivity and effective power quality solution for capacity steel, metal, mining and electrical • Improved energy efciency utilities. -

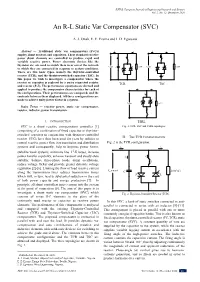

TCI) Static Var Compensator (SVC

EJERS, European Journal of Engineering Research and Science Vol. 5, No. 12, December 2020 An R-L Static Var Compensator (SVC) A. J. Onah, E. E. Ezema and I. D. Egwuatu i i i i i Abstract — Traditional static var compensators (SVCs) L S L S L iS employ shunt reactors and capacitors. These standard reactive i Com i i i com power shunt elements are controlled to produce rapid and C L variable reactive power. Power electronic devices like the L S S thyristor etc. are used to switch them in or out of the network 1 2 Load(Z) Vm sint Vmsint C Load(Z) Vmsint Load(Z) S1 S2 to which they are connected in response to system conditions. S1 S2 There are two basic types, namely the thyristor-controlled R reactor (TCR), and the thyristor-switched capacitor (TSC). In C L this paper we wish to investigate a compensator where the reactor or capacitor is replaced by a series connected resistor TCR TSC TSRL and reactor (R-L). The performance equations are derived and applied to produce the compensator characteristics for each of the configurations. Their performances are compared, and the contrasts between them displayed. All three configurations are made to achieve unity power factor in a system. Index Terms — reactive power, static var compensator, resistor, inductor, power transmission. I. INTRODUCTION1 TCR TSC TSRL SVC is a shunt reactive compensation controller [1] Fig. 1. TCR, TSC and TSRL topologies. comprising of a combination of fixed capacitor or thyristor- switched capacitor in conjunction with thyristor-controlled reactor.