SPIO-4 Precision Signal-Path Controller Board User Guide

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Dialog Semiconductor to Acquire Atmel

Filed by Atmel Corporation Pursuant to Rule 425 Under The Securities Act of 1933 And Deemed Filed Pursuant to Rule 14a-12 Under the Securities Exchange Act of 1934 Subject Company: Atmel Corporation Commission File Number: 000-19032 DIALOG SEMICONDUCTOR TO ACQUIRE ATMEL Jose Cano Head of IR Thank you, and good morning to everyone joining us today. This call is being hosted by Dialog Semiconductor's CEO, Dr. Jalal Bagherli, and we are also delighted to welcome Steve Laub, CEO of Atmel. In a moment, I will hand you over to Jalal for a review of yesterday's announcement. I must remind everyone that today's briefing and some of the answers to your questions may contain forward-looking statements in relation to Dialog and Atmel and the future operating performance of and outlook of Dialog and the combined company that are subject to risks and uncertainties. These forward-looking statements are based upon the current beliefs and expectations of the management of Dialog and Atmel, and there are risks associated with them. You can find a full explanation of these risks in the press release and the investor presentation which has been posted to the IR section of our website. Before I hand over to Jalal, let me remind you that a description of underlying performance and non-GAAP metrics has been included as well in slide 20 of the investor presentation available on our website. These financial metrics have not been calculated in accordance with IFRS or GAAP, as applicable, so you are encouraged to refer to the most comparable IFRS or GAAP financial metrics. -

0.18 Um CMOS Cell-Based ASIC Military

Features • Comprehensive Library of Standard Logic and I/O Cells • ATC18 Core and I/O Cells Designed to Operate with VDD = 1.8V ± 0.15V as Main Target Operating Conditions • IO33 Pad Libraries Provide Interfaces to 3V Environments • Memory Cells Compiled to the Precise Requirements of the Design • Compatible with Atmel’s Extensive Range of Microcontroller, DSP, Standard-interface and Application-specific Cells • EDAC Library • SEU Hardened DFF’s • Cold Sparring Buffers 0.18 µm CMOS • High Speed LVDS Buffers • PCI Buffer • Predefined die Sizes to Easily Accommodate Specified Packages Cell-based ASIC • MQFP Packages up to 352 pins (340 Signal Pins) • MCGA Packages up to 625 pins (581 Signal Pins) for Military Use • Offered to QML Q Grade Description ATC18M The Atmel ATC18M is fabricated on a proprietary 0.18 µm, up to six-layer-metal CMOS process intended for use with a supply voltage of 1.8V ± 0.15V. Table 1 shows the range for which Atmel library cells have been characterized. Advanced Table 1. Recommended Operating Conditions Information Symbol Parameter Conditions Min Typ Max Unit VDD DC Supply Voltage Core and Standard I/Os 1.65 1.8 1.95 V VDD3.3 DC Supply Voltage 3V Interface I/Os 3 3.3 3.6 V VI DC Input Voltage 0 VDD V VO DC Output Voltage 0 VDD V Operating Free Air TEMP Military -55 +125 °C Temperature Range The Atmel cell libraries and megacell compilers have been designed in order to be compatible with each other. Simulation representations exist for three types of operat- ing conditions. -

Atmel Studio 7 And

Atmel Studio 7 Part I Advanced Developer Software Deciding Development Software: ● Application Dependent: ○ Embedded Systems ○ Front end GUI ○ Databases ○ AI ○ PCB fabrication ○ Simulation ● Vendor Dependent: ○ ARM ○ Atmel ○ Etc. Arduino IDE ● Pros: ○ Light Weight ○ Works “out of the box” ○ Comes with examples and samples to help get started ○ Easy to configure with Hardware ○ Open Source ○ Add-ons for additional hardware ■ Ada Fruit ■ Sparkfun ■ Etc ● Cons: ○ Not an engineer's tool ○ Anything more complex than a Hobbyist's breadboard device can be hard to manage Atmel Studios 7 Pros: ● More professional level tools ○ Autocomplete ○ Project hierarchy ○ Simulator ○ In-System Programming and In-Circuit Emulator (ICE) support Cons: ● Much more bulky ○ Built on top of a Microsoft Visual Studios Shell. (~3GB in size) ● Another software to learn and feel familiar with. Importing Arduino Script Process: ● Make an Arduino script or take a blank one ● Go to “file” -> ”New project” -> “import Arduino Script” ○ Pick the path of desired script and Arduino IDE install path. ● Select Board type and Device type ○ For our projects these will either be “Leonardo” or “Lillypad USB” Arduino Import Hierarchy Hierarchy Cont. For Arduino projects the Hierarchy is important for showing two different things: ● Arduino Base Code ○ Looking into the base code is important for finding microcontroller specific defaults. ● Better Organize your project source files ○ Main Script ○ Headers/ Src. Simulator ● Similar to AVR Studio 4’s simulator, used in EE346, the Atmel Studio 7 simulator provides a quick method of verifying your code. ○ Go to “tools” as seen in the toolbar the select “debugger” -> “simulator” ○ Same as other simulators, utilize the stepping tools as needed. -

AVR XMEGA C3 Device Datasheet

8/16-bit Atmel XMEGA C3 Microcontroller ATxmega384C3 Features High-performance, low-power Atmel® AVR® XMEGA® 8/16-bit Microcontroller Nonvolatile program and data memories 384KBytes of in-system self-programmable flash 8KBytes boot section 4KBytes EEPROM 32KBytes internal SRAM Peripheral features Two -channel DMA controller Four-channel event system Five 16-bit timer/counters Four timer/counters with four output compare or input capture channels One timer/counter with two output compare or input capture channels High resolution extension on two timer/counters Advanced waveform extension (AWeX) on one timer/counter One USB device interface USB 2.0 full speed (12Mbps) and low speed (1.5Mbps) device compliant 32 Endpoints with full configuration flexibility Three USARTs with IrDA support for one USART Two two-wire interfaces with dual address match (I2C and SMBus compatible) Two serial peripheral interfaces (SPIs) AES crypto engine CRC-16 (CRC-CCITT) and CRC-32 (IEEE®802.3) generator 16-bit real time counter (RTC) with separate oscillator One sixteen-channel, 12-bit, 300ksps Analog to Digital Converter Two Analog Comparators with window compare function, and current sources External interrupts on all general purpose I/O pins Programmable watchdog timer with separate on-chip ultra low power oscillator QTouch® library support Capacitive touch buttons, sliders and wheels Special microcontroller features Power-on reset and programmable brown-out detection Internal and external clock options with PLL and prescaler Programmable multilevel interrupt controller Five sleep modes Programming and debug interface PDI (program and debug interface) I/O and packages 50 programmable I/O pins 64-lead TQFP 64-pad QFN Operating voltage 1.6 – 3.6V Operating frequency 0 – 12MHz from 1.6V 0 – 32MHz from 2.7V Atmel-8361G-AVR-ATxmega384C3-Datasheet–06/2015 1. -

Fast Software AES Encryption

Fast Software AES Encryption Dag Arne Osvik1 Joppe W. Bos1 Deian Stefan2 David Canright3 1Laboratory for Cryptologic Algorithms, EPFL, CH-1015 Lausanne, Switzerland 2Dept. of Electrical Engineering, The Cooper Union, NY 10003, New York, USA 3Applied Math., Naval Postgraduate School, Monterey CA 93943, USA 1 / 20 Fast Software AES Encryption Dag Arne Osvik1 Joppe W. Bos1 Deian Stefan2 David Canright3 Presented by: Onur Ozen¨ 1 1Laboratory for Cryptologic Algorithms, EPFL, CH-1015 Lausanne, Switzerland 2Dept. of Electrical Engineering, The Cooper Union, NY 10003, New York, USA 3Applied Math., Naval Postgraduate School, Monterey CA 93943, USA 1 / 20 Outline Introduction Motivation Related Work Contributions The Advanced Encryption Standard Target Platforms The 8-bit AVR Microcontroller The 32-bit Advanced RISC Machine The Cell Broadband Engine Architecture The NVIDIA Graphics Processing Unit Conclusions 2 / 20 Motivation Advanced Encryption Standard Rijndael announced in 2001 as the AES. One of the most widely used cryptographic primitives. IP Security, Secure Shell, Truecrypt RFID and low-power authentication methods Key tokens, RF-based Remote Access Control Many intensive efforts to speed up AES in both hard- and software. Related work E. K¨asper and P. Schwabe. Faster and Timing-Attack Resistant AES-GCM. CHES 2009. P. Bulens, et al. Implementation of the AES-128 on Virtex-5 FPGAs AFRICACRYPT 2008. O. Harrison and J. Waldron. Practical Symmetric Key Cryptography on Modern Graphics Hardware. USENIX Sec. Symp. 2008. S. Rinne, et al. Performance Analysis of Contemporary Light-Weight Block Ciphers on 8-bit Microcontrollers. SPEED 2007. K. Shimizu, et al. Cell Broadband Engine Support for Privacy, Security, and Digital Rights Management Applications. -

Atmel AT91FR4081 Datasheet

Features • Incorporates the ARM7TDMI™ ARM® Thumb® Processor Core – High-performance 32-bit RISC Architecture – High-density 16-bit Instruction Set – Leader in MIPS/Watt – Embedded ICE (In-circuit Emulation) • 136K Bytes of On-chip SRAM – 32-bit Data Bus, Single-clock Cycle Access • 512K Words 16-bit Flash Memory (8 Mbits) – Single Voltage Read/Write, 110 ns Access Time ® – Sector Erase Architecture AT91 ARM – Fast Word Program Time of 20 µs; Fast Sector Erase Time of 200 ms – Dual-plane Organization Allows Concurrent Read and Program/Erase ® – Erase Suspend Capability Thumb – Low-power Operation: 25 mA Active, 10 µA Standby – Data Polling, Toggle Bit and Ready/Busy End of Program Cycle Detection Microcontrollers – Reset Input for Device Initialization – Sector Program Unlock Command – Factory-programmed AT91 Flash Uploader Software • Fully Programmable External Bus Interface (EBI) AT91FR4081 – Up to 8 Chip Selects, Maximum External Address Space of 64M Bytes – Software Programmable 8/16-bit External Data Bus • 8-level Priority, Individually Maskable, Vectored Interrupt Controller – 4 External Interrupts, Including a High-priority Low-latency Interrupt Request • 32 Programmable I/O Lines • 3-channel 16-bit Timer/Counter – 3 External Clock Inputs – 2 Multi-purpose I/O Pins per Channel • 2USARTs – 2 Dedicated Peripheral Data Controller (PDC) Channels per USART • Programmable Watchdog Timer • Advanced Power-saving Features – CPU and Peripherals Can be De-activated Individually • Fully Static Operation: – 0 Hz to 33 MHz Internal Frequency Range at 3.0V, 85°C • 2.7V to 3.6V Operating Range • -40°Cto85°C Temperature Range • Available in a 120-ball BGA Package Description The AT91FR4081 is a member of the Atmel AT91 16/32-bit Microcontroller family, which is based on the ARM7TDMI processor core. -

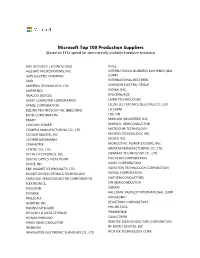

Microsoft Top 100 Production Suppliers (Based on FY14 Spend for Commercially Available Hardware Products)

Microsoft Top 100 Production Suppliers (Based on FY14 spend for commercially available hardware products) AAC ACOUSTIC TECHNOLOGIES INTEL ALLEGRO MICROSYSTEMS, INC. INTERNATIONAL BUSINESS MACHINES (IBM ALPS ELECTRIC COMPANY CORP.) AMD INTERNATIONAL RECTIFIER AMPEREX TECHNOLOGY, LTD. JOHNSON ELECTRIC GROUP AMPHENOL KIONIX, INC. ANALOG DEVICES KYOCERA/AVX ASKEY COMPUTER CORPORATION LAIRD TECHNOLOGIES ATMEL CORPORATION LELON ELECTRONICS (SUZHOU) CO., LTD BIZLINK TECHNOLOGY INC (BIZCONN) LG CHEM BOYD CORPORATION LITE-ON BRADY MARLOW INDUSTRIES, INC. CHICONY POWER MARVELL SEMICONDUCTOR COMPEQ MANUFACTURING CO., LTD. MICROCHIP TECHNOLOGY COOLER MASTER, INC. MICRON TECHNOLOGY, INC. COOPER BUSSMANN MOLEX, INC. CYMMETRIK MONOLITHIC POWER SYSTEMS, INC. CYNTEC CO., LTD. MURATA MANUFACTURING CO., LTD. DELTA ELECTRONICS, INC. NEWMAX TECHNOLOGY CO., LTD. DIGITAL OPTICS VISTA POINT NICHICON CORPORATION DIODE, INC. NIDEC CORPORATION E&E MAGNETICS PRODUCTS, LTD. NUVOTON TECHNOLOGY CORPORATION ELLINGTON ELECTRONICS TECHNOLOGY NVIDIA CORPORATION FAIRCHILD SEMICONDUCTOR CORPORATION NXP SEMICONDUCTORS FLEXTRONICS ON SEMICONDUCTOR FOXCONN OSRAM FOXLINK PALCONN, PALPILOT INTERNATIONAL CORP. FREESCALE PANASONIC GOERTEK, INC. PEGATRON CORPORATION HANNSTAR BOARD PHILIPS PLDS HITACHI-LG DATA STORAGE PRIMESENSE HONDA PRINTING QUALCOMM HYNIX SEMICONDUCTOR REALTEK SEMICONDUCTOR CORPORATION INFINEON RF MICRO DEVICES, INC. INNOVATOR ELECTRONIC SHENZHEN CO., LTD RICHTEK TECHNOLOGY CORP. ROHM CORPORATION SAMSUNG DISPLAY SAMSUNG ELECTRONICS SAMSUNG SDI SAMSUNG SEMICONDUCTOR SEAGATE SHEN ZHEN JIA AI MOTOR CO., LTD. SHENZHEN HORN AUDIO CO., LTD. SHINKO ELECTRIC INDUSTRIES CO., LTD. STARLITE PRINTER, LTD. STMICROELECTRONICS SUNG WEI SUNUNION ENVIRONMENTAL PACKAGING CO., LTD TDK TE CONNECTIVITY TEXAS INSTRUMENTS TOSHIBA TPK TOUCH SOLUTIONS, INC. UNIMICRON TECHNOLOGY CORP. UNIPLAS (SHANGHAI) CO., LTD. UNISTEEL UNIVERSAL ELECTRONICS INCORPORATED VOLEX WACOM CO., LTD. WELL SHIN TECHNOLOGY WINBOND WOLFSON MICROELECTRONICS, LTD. X-CON ELECTRONICS, LTD. YUE WAH CIRCUITS CO., LTD. -

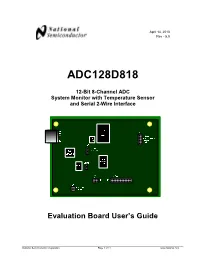

12-Bit 8-Channel ADC System Monitor with Temp Sensor and Serial 2

ADC128D818 Evaluation Board User’s Guide April 14, 2010 Rev - 5.0 ADC128D818 12-Bit 8-Channel ADC System Monitor with Temperature Sensor and Serial 2-Wire Interface Evaluation Board User’s Guide National Semiconductor Corporation Page 1 of 18 www.national.com ADC128D818 Evaluation Board User’s Guide This Page Intentionally Left Blank National Semiconductor Corporation Page 2 of 18 www.national.com ADC128D818 Evaluation Board User’s Guide Table of Contents 1. Introduction……………………………………………………………………………………………………. 4 2. Quick Start……………….…………………………………………………………………………………….. 4 2.1 Setting Up the Board..…………..………………………………………………………………..……... 4 2.2 Starting the Software………..………………………………………………………………..…..……... 4 3. Equipment Setup………………………………………………………………………………………………. 5 3.1 Equipment List…………………………………………………………………………………............... 5 2.2 Equipment Connection Diagram ………………………………………………………………………. 5 4. ADC128D818 Board Setup……………………………………………………………………………………6 4.1 Component Placement Diagram…………………………………………………............................... 6 4.2 Jumper Options………………………………………………………………………………………….. 7 4.3 Powering the Board…………………………………………………………………………………….. 8 5. SensorEval Software………………………………………………………………………………………….. 9 5.1 Installing the Software…………..………………………………………………………………..……... 9 5.2 Setting the Address.……..………………………………………………………………..…..…….......9 5.3 ADC128D818 Registers………..…………………………………………………………..…..…….....10 6. Appendix………………………………………………………………………………………………………...12 6.1 Board Schematic…………..…………………………………………………………………….............12 6.2 Board Layouts……….……..……………………………………………………………………............14 -

AVR-Iot WG User Guide AVR-Iot WG Development Board User Guide

AVR-IoT WG User Guide AVR-IoT WG Development Board User Guide Preface The AVR-IoT WG development board is a small and easily expandable demonstration and development platform for IoT solutions, based on the AVR® microcontroller architecture using Wi-Fi® technology. It was designed to demonstrate that the design of a typical IoT application can be simplified by partitioning the problem into three blocks: • Smart - represented by the ATmega4808 microcontroller • Secure - represented by the ATECC608A secure element • Connected - represented by the WINC1510 Wi-Fi controller module The AVR-IoT WG development board features a USB interface chip Nano Embedded Debugger (nEDBG) that provides access to a serial port interface (serial to USB bridge), a mass storage interface for easy ‘drag and drop’ programming, configuration and full access to the AVR microcontroller UPDI interface for programming and debugging directly from Microchip MPLAB® X IDE and the Atmel® Studio 7.0 IDE. The AVR-IoT WG development board comes preprogrammed and configured for demonstrating connectivity to the Google Cloud IoT Core. The AVR-IoT WG development board features two sensors: • A light sensor • A high-accuracy temperature sensor - MCP9808 Additionally, a mikroBUS™ connector is provided to expand the board capabilities with 450+ sensors and actuators offered by MikroElektronika (www.mikroe.com) via a growing portfolio of Click boards™. © 2018 Microchip Technology Inc. User Guide DS50002809A-page 1 AVR-IoT WG User Guide Table of Contents Preface........................................................................................................................... -

ATMEL Atmega8 Microcontroller

Features • High-performance, Low-power Atmel®AVR® 8-bit Microcontroller • Advanced RISC Architecture – 130 Powerful Instructions – Most Single-clock Cycle Execution – 32 × 8 General Purpose Working Registers – Fully Static Operation – Up to 16MIPS Throughput at 16MHz – On-chip 2-cycle Multiplier • High Endurance Non-volatile Memory segments – 8Kbytes of In-System Self-programmable Flash program memory – 512Bytes EEPROM 8-bit Atmel with – 1Kbyte Internal SRAM – Write/Erase Cycles: 10,000 Flash/100,000 EEPROM – Data retention: 20 years at 85°C/100 years at 25°C(1) 8KBytes In- – Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program System True Read-While-Write Operation – Programming Lock for Software Security Programmable • Peripheral Features – Two 8-bit Timer/Counters with Separate Prescaler, one Compare Mode Flash – One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode – Real Time Counter with Separate Oscillator – Three PWM Channels ATmega8 – 8-channel ADC in TQFP and QFN/MLF package Eight Channels 10-bit Accuracy ATmega8L – 6-channel ADC in PDIP package Six Channels 10-bit Accuracy – Byte-oriented Two-wire Serial Interface – Programmable Serial USART – Master/Slave SPI Serial Interface – Programmable Watchdog Timer with Separate On-chip Oscillator – On-chip Analog Comparator • Special Microcontroller Features – Power-on Reset and Programmable Brown-out Detection – Internal Calibrated RC Oscillator – External and Internal Interrupt Sources – Five Sleep Modes: Idle, -

Atmel Studio

Software Atmel Studio USER GUIDE Preface Atmel® Studio is an Integrated Development Environment (IDE) for writing and debugging AVR®/ARM® applications in Windows® XP/Windows Vista®/ Windows 7/8 environments. Atmel Studio provides a project management tool, source file editor, simulator, assembler, and front-end for C/C++, programming, and on-chip debugging. Atmel Studio supports the complete range of Atmel AVR tools. Each new release contains the latest updates for the tools as well as support for new AVR/ARM devices. Atmel Studio has a modular architecture, which allows interaction with 3rd party software vendors. GUI plugins and other modules can be written and hooked to the system. Contact Atmel for more information. Atmel-42167B-Atmel-Studio_User Guide-09/2016 Table of Contents Preface............................................................................................................................ 1 1. Introduction................................................................................................................8 1.1. Features....................................................................................................................................... 8 1.2. New and Noteworthy.................................................................................................................... 8 1.2.1. Atmel Studio 7.0............................................................................................................ 8 1.2.2. Atmel Studio 6.2 Service Pack 2..................................................................................11 -

Dragonboard™ 410C Based on Qualcomm® Snapdragon™ 410E Processor Peripherals Programming Guide Linux Android

Qualcomm Technologies, Inc. DragonBoard™ 410c based on Qualcomm® Snapdragon™ 410E processor Peripherals Programming Guide Linux Android LM80-P0436-5 Rev F September 2016 © 2015-2016 Qualcomm Technologies, Inc. All rights reserved. MSM and Qualcomm Snapdragon are products of Qualcomm Technologies, Inc. Other Qualcomm products referenced herein are products of Qualcomm Technologies, Inc. or its other subsidiaries. DragonBoard, MSM, Qualcomm and Snapdragon are trademarks of Qualcomm Incorporated, registered in the United States and other countries. Other product and brand names may be trademarks or registered trademarks of their respective owners. This technical data may be subject to U.S. and international export, re-export, or transfer (“export”) laws. Diversion contrary to U.S. and international law is strictly prohibited. Use of this document is subject to the license set forth in Exhibit 1. Questions or comments: https://www.96boards.org/DragonBoard410c/forum Qualcomm Technologies, Inc. 5775 Morehouse Drive San Diego, CA 92121 U.S.A. LM80-P0436-5 Rev F Revision history Revision Date Description F September 2016 Updated to ‘E’ part. E December 2015 Fixed BLSP address table for SPI for APQ8016 Added info for UART baud rates in 3.1.2 and I2C core in 4.1.1; fixed a D August 28, 2015 lunch command typo, removed / in the path for kernel C June 1, 2015 Added details to BLSP in section 3. B May 20, 2015 Updated Revision history and © date for Rev B. A April 2015 Initial release. LM80-P0436-5 Rev F MAY CONTAIN U.S. AND INTERNATIONAL EXPORT CONTROLLED INFORMATION 2 Contents 1 Introduction ..........................................................................................................................