Ce1901 Laboratory Project

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Disability Classification System

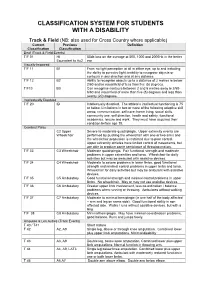

CLASSIFICATION SYSTEM FOR STUDENTS WITH A DISABILITY Track & Field (NB: also used for Cross Country where applicable) Current Previous Definition Classification Classification Deaf (Track & Field Events) T/F 01 HI 55db loss on the average at 500, 1000 and 2000Hz in the better Equivalent to Au2 ear Visually Impaired T/F 11 B1 From no light perception at all in either eye, up to and including the ability to perceive light; inability to recognise objects or contours in any direction and at any distance. T/F 12 B2 Ability to recognise objects up to a distance of 2 metres ie below 2/60 and/or visual field of less than five (5) degrees. T/F13 B3 Can recognise contours between 2 and 6 metres away ie 2/60- 6/60 and visual field of more than five (5) degrees and less than twenty (20) degrees. Intellectually Disabled T/F 20 ID Intellectually disabled. The athlete’s intellectual functioning is 75 or below. Limitations in two or more of the following adaptive skill areas; communication, self-care; home living, social skills, community use, self direction, health and safety, functional academics, leisure and work. They must have acquired their condition before age 18. Cerebral Palsy C2 Upper Severe to moderate quadriplegia. Upper extremity events are Wheelchair performed by pushing the wheelchair with one or two arms and the wheelchair propulsion is restricted due to poor control. Upper extremity athletes have limited control of movements, but are able to produce some semblance of throwing motion. T/F 33 C3 Wheelchair Moderate quadriplegia. Fair functional strength and moderate problems in upper extremities and torso. -

Presenting the Paralympics: Affective Nationalism and the 'Able-Disabled'

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Bournemouth University Research Online (Re-)presenting the Paralympics: Affective Nationalism and the 'able-disabled' Emma Pullen, Daniel Jackson and Michael Silk Communication & Sport (2019, in press) *To cite this article: Pullen, E., Jackson, D., and Silk, M. (2019). (Re-)presenting the Paralympics: Affective Nationalism and the 'able-disabled'. Communication & Sport Corresponding author: [email protected] Abstract The relationship between media, sport, nations and nationalism is well established, yet, there is an absence of these discussions at the intersection of communication, Paralympics and disability studies. This omission is particularly significant considering the rapid commodification of the Paralympic spectacle, exacerbated by the entry of Channel 4 (C4) as the UK Paralympic rights holders, that has seen the games become an important site of disability (re-)presentation. In this article, we focus on the construction of national, normative, disabled bodies in Paralympic representation drawn from an analysis of three integrated datasets from Channel 4’s broadcasting of the Rio 2016 Paralympics: interviews with C4 production and editorial staff; quantitative content analysis, and qualitative moving image analysis. We highlight the strategic approach taken by C4 to focus on successful medal winning athletes; the implications this has on the sports and disability classifications given media coverage; and the role of affective high-value production practices. We also reveal the commercial tensions and editorial decisions that broadcasters face with respect to which disabilities / bodies are made hyper-visible - and thereby those which are marginalized - as national disability sport icons that inculcate preferred notions of disability and the (re)imagined nation. -

World Para Nordic Skiing WC Points Winter Season 2019/20

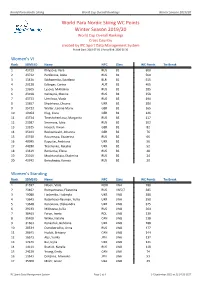

World Para Nordic Skiing World Cup Overall Rankings Winter Season 2019/20 World Para Nordic Skiing WC Points Winter Season 2019/20 World Cup Overall Rankings Cross Country created by IPC Sport Data Management System Period Start: 2019-07-01 | Period End: 2020-06-30 Women's VI Rank SDMS ID Name NPC Class WC Points Tie Break 1 43739 Khlyzova, Vera RUS B2 600 2 43732 Panferova, Anna RUS B2 560 3 13436 Sakhanenka, Sviatlana BLR B2 515 4 29128 Edlinger, Carina AUT B1 405 5 13605 Lysova, Mikhalina RUS B2 285 6 23918 Galitsyna, Marina RUS B1 258 7 43733 Umrilova, Vlada RUS B3 190 8 13657 Shyshkova, Oksana UKR B2 180 9 35723 Walter, Leonie Maria GER B2 165 10 19064 Klug, Clara GER B1 126 11 43734 Tereshchenkova, Margarita RUS B3 117 12 23987 Smirnova, Iuliia RUS B2 102 13 13525 Hoesch, Vivian GER B1 82 14 35103 Recktenwald, Johanna GER B2 76 15 43740 Razumnaia, Ekaterina RUS B2 66 16 40995 Kapustei, Andriana UKR B2 56 17 44280 Tkachenko, Nataliia UKR B2 52 18 13619 Remizova, Elena RUS B3 48 19 23919 Moshkovskaia, Ekaterina RUS B2 24 20 43742 Berezhnaia, Kseniia RUS B2 20 Women's Standing Rank SDMS ID Name NPC Class WC Points Tie Break 1 31597 Nilsen, Vilde NOR LW4 780 2 23402 Rumyantseva, Ekaterina RUS LW5/7 385 3 19080 Liashenko, Liudmyla UKR LW8 380 4 13643 Batenkova-Bauman, Yuliia UKR LW6 350 5 13648 Kononova, Oleksandra UKR LW8 325 6 29233 Mikheeva, Iuliia RUS LW8 264 7 30463 Faron, Iweta POL LW8 239 8 35400 Wilkie, Natalie CAN LW8 238 9 31663 Konashuk, Bohdana UKR LW8 188 10 20534 Ostroborodko, Anna RUS LW8 177 11 20641 Hudak, Brittany CAN -

The Impact of Lower-Limb Prosthetic Limb Use in International C4 Track Para-Cycling

The impact of lower-limb prosthetic limb use in international C4 track para-cycling An investigation was undertaken to ascertain any impact or significance of athletes within the C4 paracycling classification between those who use a lower- limb prostheses and those who do not. A statistical evaluation of event completion time was undertaken to assess C4 cyclists when competing at the World Championships and the Paralympic Games in the 1km track time trial. The C4 athletes who utilise a prostheses consistently outperformed non-amputees in the C4 classification from 2011-2016 on a competition-to-competition basis. However, when the participations were grouped as a whole together and an identified outlier athlete was removed, it was then demonstrated that there was no statistical significance between those who required the use of a lower-limb prostheses to those that did not when either evaluated on a competition-by- competition or on an amputee and non-amputee group-by-group basis (P=>0.05). As a result, this study proposes that those requiring the use of lower-limb prostheses are neither advantaged nor disadvantaged in the C4 classification category when competing in the 1km time trial at this time. Implications for Rehabilitation • This analysis indicates that at this time, there is no evidence to suggest that use of such technology is advantageous in this category or should be seen as controversial. • The design of lower-limb prosthetic limb technology in cycling should continue to be developed and optimized unabated. • This study begins to address the cited lack of peer reviewed information regarding paracycling with limb absence available to practitioners. -

World Para Alpine Skiing WC Points Winter Season 2020/21

World Para Alpine Skiing World Cup Individual Rankings Winter Season 2020/21 World Para Alpine Skiing WC Points Winter Season 2020/21 World Cup Individual Rankings created by IPC Sport Data Management System Period Start: 2020-07-01 | Period End: 2021-06-30 Women's Slalom VI Rank SDMS ID Name NPC Class WC Points Tie Break 1 23842 Ristau, Noemi Ewa GER B2 220 2 22142 Aigner, Veronika AUT B2 200 3 40290 Aigner, Barbara AUT B3 180 4 44235 Rexova, Alexandra SVK B2 160 5 31601 Bennink, Maaike NED B2 60 6 13349 Farkasova, Henrieta SVK B3 50 Women's Slalom Standing Rank SDMS ID Name NPC Class WC Points Tie Break 1 29162 Rieder, Anna-Maria GER LW9-1 260 2 13162 Rothfuss, Andrea GER LW6/8-2 210 3 29136 Voronchikhina, Varvara RUS LW6/8-2 180 4 13116 Bochet, Marie FRA LW6/8-2 140 5 24067 Smetisko, Lucija CRO LW6/8-2 120 6 41102 Aarsjoe, Ebba SWE LW4 100 7 14585 Khorosheva, Anastasiia RUS LW9-2 50 8 42372 Richard, Aurelie FRA LW6/8-2 45 Women's Slalom Sitting Rank SDMS ID Name NPC Class WC Points Tie Break 1 13161 Forster, Anna-Lena GER LW12-1 400 2 21797 van Bergen, Barbara NED LW11 80 Men's Slalom VI Rank SDMS ID Name NPC Class WC Points Tie Break 1 13724 Deleplace, Hyacinthe FRA B2 230 2 20881 Bertagnolli, Giacomo ITA B3 200 24.30 (§302.3) 3 35366 Simpson, Neil GBR B3 200 35.60 (§302.3) 4= 40291 Aigner, Johannes AUT B2 160 4= 13338 Krako, Jakub SVK B2 160 6 13335 Haraus, Miroslav SVK B2 105 7 44167 Scharnagl, Michael AUT B3 100 IPC Sport Data Management System Page 1 of 7 26 September 2021 at 01:38:04 CEST World Para Alpine Skiing World Cup Individual -

START LIST As of 11 DEC 2017

CROSS COUNTRY LONG DISTANCE START LIST As of 11 DEC 2017 NPC Sport Start IPCNS WC Bib Name Code Class % Time Points Points Remarks Women Long C,Sitting 1 IOVLEVA Mariia NPA LW12 100 10:00:30 82 2 GULIAEVA Irina NPA LW12 100 10:01:00 81 3 ZHANG Lei CHN LW12 100 10:01:30 38 4 ABDIKARIMOVA Akzhana NPA LW10.5 90 10:02:00 48 5 FEDOROVA Nadezhda NPA LW12 100 10:02:30 45 6 ZAINULLINA Marta NPA LW12 100 10:03:00 140 7 KOCHEROVA Natalia NPA LW12 100 10:03:30 55 8 dos SANTOS ROCHA Aline BRA LW11 94 10:04:00 339.52 31 9 BALTABAYEVA Zhanyl KAZ LW12 100 10:04:30 228.48 10 LEE Do Yeon KOR LW12 100 10:05:00 226.20 15 11 GRETSCH Kendall USA LW11.5 96 10:05:30 160.33 64 12 SEO Vo-Ra-Mi KOR LW10.5 90 10:06:00 131.27 38 13 NAN Yuyu CHN LW11 94 10:06:30 113.22 20 14 JIN Yawei CHN LW10 86 10:07:00 73.85 56 15 CHU Beibei CHN LW12 100 10:07:30 58.47 65 16 SKARSTEIN Birgit NOR LW11 94 10:08:00 26.12 110 17 MASTERS Oksana USA LW12 100 10:08:30 0.00 120 18 ESKAU Andrea (WL) GER LW11 94 10:09:00 1.71 200 Men Long C,Sitting 21 RIBERA Cristian BRA LW11 94 10:40:30 24 22 HUANG Feixiang CHN LW12 100 10:41:00 30 23 GANZEI Aleksandr NPA LW12 100 10:41:30 68 24 KADENOV Suyundyk KAZ LW12 100 10:42:00 25 ZHENG Peng CHN LW10 86 10:42:30 82 26 LIM Woo Geun KOR LW11 94 10:43:00 27 FURUBERG Arnt Christian SWE LW11.5 96 10:43:30 15 28 WAGNER Jeremy USA LW11.5 96 10:44:00 21 29 AMINOV Rustam NPA LW10 86 10:44:30 9 30 PETUSHKOV Roman NPA LW12 100 10:45:00 53 31 FRAZIER Eric USA LW11 94 10:45:30 32 DAVIDOVICH Aleksandr NPA LW12 100 10:46:00 125 33 ROCHA Fernando BRA LW11.5 96 10:46:30 -

OFFICIAL RESULTS As of 13 DEC 2018

SALASTRAINS ST. MORITZ 2019 WPAS EUROPA CUP MEN'S GIANT SLALOM 1 THU 13 DEC 2018 13:30 FINAL OFFICIAL RESULTS As of 13 DEC 2018 Jury Technical Data IPC/FIS Technical Delegate GURZELER Thomas SUI Course Name Salastrains Referee SKUTELJ Anja CRO Start Altitude 2360 m Chief of Race KUENZLER Sandro SUI Finish Altitude 2040 m Vertical Drop 320 m Homologation Number 12125/10/16 Timing device VOLA Race Information 1st Run Race Information 2nd Run Course Setter CHAMBAZ Gregory SUI Course Setter WOLF Justus GER Number of Gates 37 Number of Gates 37 Turning Gates 35 Turning Gates 36 Start Time 10:10 Start Time 13:30 Forerunners A-CAROLA C SUI Forerunners A-CAROLA C SUI B-ZALA A SUI B-ZALA A SUI WEATHER DATA At Start At Finish At Start At Finish Weather Clear sky Clear sky Snow Compact Compact Temperature -15.0 ºC -15.0 ºC Penalty: 10.09 F-Value: 870 IPC/FIS codex: 0849 Number of Competitors: 67, Number of NPCs: 23 Sport NPC Race EC Rank Bib Name 1st RUN 2nd RUN Result Diff. Class Code Pts. Pts. Men Giant Slalom Vision Impaired 1 1 27 KUBACKA Marek B1 SVK 53.78 (3) 52.39 (1) 1:46.17 47.81 100 Guide: ZATOVICOVA Maria 2 31 HARAUS Miroslav B2 SVK 54.16 (4) 52.40 (2) 1:46.56 +0.39 51.18 80 Guide: HUDIK Maros 3 26 SANTACANA MAIZTEGUI Yon B2 ESP 55.67 (5) 55.87 (5) 1:51.54 +5.37 94.23 60 Guide: GALINDO GARCES M 4 38 SIMPSON Neil B3 GBR 57.79 (6) 55.62 (3) 1:53.41 +7.24 110.39 50 Guide: ROBERTSON Jamie 5 28 BURTON Kevin B2 USA 57.84 (7) 55.72 (4) 1:53.56 +7.39 111.69 45 Guide: GRIMMELMANN Kurt 6 33 MORGENFURT Gernot B2 AUT 57.95 (8) 57.21 (6) 1:55.16 +8.99 -

OFFICIAL RESULTS As of 7 NOV 2019

SNOWWORLD LANDGRAAF 2020 WORLD PARA ALPINE SKIING EC WOMEN'S SLALOM 1 THU 7 NOV 2019 13:15 FINAL OFFICIAL RESULTS As of 7 NOV 2019 Jury Technical Data IPC/FIS Technical Delegate GAYRAUD Bernard GRE Course Name Landgraaf1 WPAS Race Director SKUTELJ Anja IPC Start Altitude 219 m Referee TEITSMA Falco NED Finish Altitude 156 m Chief of Race OOSTDJIK Martijn NED Vertical Drop 63 m Homologation Number 11352/09/14 Timing device Alge TDC 8001 Race Information 1st Run Race Information 2nd Run Race Information 3rd Run Course Setter NAZAROV Alex RUS Course Setter BERQUIST H SWE Course Setter NAZAROV Alex RUS Number of Gates 34 Number of Gates 35 Number of Gates 34 Turning Gates 31 Turning Gates 34 Turning Gates 31 Start Time 09:00 Start Time 12:00 Start Time 13:15 Forerunners A- MARTIN-GRANIZOESP FE. Forerunners A- MARTIN-GRANIZOESP FE. Forerunners A- MARTIN-GRANIZOESP FE. B- BAUMANN M USA B- BAUMANN M USA B- BAUMANN M USA WEATHER DATA At Start At Finish At Start At Finish At Start At Finish Weather Clear sky Clear sky Clear sky Clear sky Clear sky Clear sky Snow Hard packed Hard packed Hard packed Hard packed Hard packed Hard packed Temperature -5.0 ºC -5.0 ºC -5.0 ºC -5.0 ºC -5.0 ºC -5.0 ºC Penalty: 23.16 F-Value: 610 IPC/FIS codex: 7010 Number of Competitors: 35, Number of NPCs: 13 Sport NPC Race EC Rank Bib Name 1st RUN 2nd RUN 3rd RUN Result Diff. Class Code Pts. Pts. -

National Classification? 13

NATIONAL CL ASSIFICATION INFORMATION FOR MULTI CLASS SWIMMERS Version 1.2 2019 PRINCIPAL PARTNER MAJOR PARTNERS CLASSIFICATION PARTNERS Version 1.2 2019 National Swimming Classification Information for Multi Class Swimmers 1 CONTENTS TERMINOLOGY 3 WHAT IS CLASSIFICATION? 4 WHAT IS THE CLASSIFICATION PATHWAY? 4 WHAT ARE THE ELIGIBLE IMPAIRMENTS? 5 CLASSIFICATION SYSTEMS 6 CLASSIFICATION SYSTEM PARTNERS 6 WHAT IS A SPORT CLASS? 7 HOW IS A SPORT CLASS ALLOCATED TO AN ATHLETE? 7 WHAT ARE THE SPORT CLASSES IN MULTI CLASS SWIMMING? 8 SPORT CLASS STATUS 11 CODES OF EXCEPTION 12 HOW DO I CHECK MY NATIONAL CLASSIFICATION? 13 HOW DO I GET A NATIONAL CLASSIFICATION? 13 MORE INFORMATION 14 CONTACT INFORMATION 16 Version 1.2 2019 National Swimming Classification Information for Multi Class Swimmers 2 TERMINOLOGY Assessment Specific clinical procedure conducted during athlete evaluation processes ATG Australian Transplant Games SIA Sport Inclusion Australia BME Benchmark Event CISD The International Committee of Sports for the Deaf Classification Refers to the system of grouping athletes based on impact of impairment Classification Organisations with a responsibility for administering the swimming classification systems in System Partners Australia Deaflympian Representative at Deaflympic Games DPE Daily Performance Environment DSA Deaf Sports Australia Eligibility Criteria Requirements under which athletes are evaluated for a Sport Class Evaluation Process of determining if an athlete meets eligibility criteria for a Sport Class HI Hearing Impairment ICDS International Committee of Sports for the Deaf II Intellectual Impairment Inas International Federation for Sport for Para-athletes with an Intellectual Disability General term that refers to strategic initiatives that address engagement of targeted population Inclusion groups that typically face disadvantage, including people with disability. -

United States Olympic Committee and U.S. Department of Veterans Affairs

SELECTION STANDARDS United States Olympic Committee and U.S. Department of Veterans Affairs Veteran Monthly Assistance Allowance Program The U.S. Olympic Committee supports Paralympic-eligible military veterans in their efforts to represent the USA at the Paralympic Games and other international sport competitions. Veterans who demonstrate exceptional sport skills and the commitment necessary to pursue elite-level competition are given guidance on securing the training, support, and coaching needed to qualify for Team USA and achieve their Paralympic dreams. Through a partnership between the United States Department of Veterans Affairs and the USOC, the VA National Veterans Sports Programs & Special Events Office provides a monthly assistance allowance for disabled Veterans of the Armed Forces training in a Paralympic sport, as authorized by 38 U.S.C. § 322(d) and section 703 of the Veterans’ Benefits Improvement Act of 2008. Through the program the VA will pay a monthly allowance to a Veteran with a service-connected or non-service-connected disability if the Veteran meets the minimum VA Monthly Assistance Allowance (VMAA) Standard in his/her respective sport and sport class at a recognized competition. Athletes must have established training and competition plans and are responsible for turning in monthly and/or quarterly forms and reports in order to continue receiving the monthly assistance allowance. Additionally, an athlete must be U.S. citizen OR permanent resident to be eligible. Lastly, in order to be eligible for the VMAA athletes must undergo either national or international classification evaluation (and be found Paralympic sport eligible) within six months of being placed on the allowance pay list. -

Para Cycling Information Sheet About the Sport Classification Explained

Para cycling information sheet About the sport Para cycling is cycling for people with impairments resulting from a health condition (disability). Para athletes with physical impairments either compete on handcycles, tricycles or bicycles, while those with a visual impairment compete on tandems with a sighted ‘pilot’. Para cycling is divided into track and road events, with seven events in total. Classification explained In Para sport classification provides the structure for fair and equitable competition to ensure that winning is determined by skill, fitness, power, endurance, tactical ability and mental focus – the same factors that account for success in sport for able-bodied athletes. The Para sport classification assessment process identifies the eligibility of each Para athlete’s impairment, and groups them into a sport class according to the degree of activity limitation resulting from their impairment. Classification is sport-specific as an eligible impairment affects a Para athlete’s ability to perform in different sports to a different extent. Each Para sport has a different classification system. Standard Classification in detail Para-Cycling sport classes include: Handcycle sport classes H1 – 5: There are five different sport classes for handcycle racing. The lower numbers indicate a more severe activity limitation. Para athletes competing in the H1 classes have a complete loss of trunk and leg function and limited arm function, e.g. as a result of a spinal cord injury. Para athletes in the H4 class have limited or no leg function, but good trunk and arm function. Para cyclists in sport classes H1 – 4 compete in a reclined position. Para cyclists in the H5 sport class sit on their knees because they are able to use their arms and trunk to accelerate the handcycle. -

List Biathlon Middle Distance

BIATHLON MIDDLE DISTANCE START LIST As of 27 JAN 2018 NPC Sport Start IPCNS WC Bib Name Code Class % Time S1 S2 S3 S4 T Points Points Time Women Middle,Visually Impaired 1 REMIZOVA Elena NPA B3 100 09:30:30 111.04 320 Guide: TOKAREV Andrei 2 GALITSYNA Marina NPA B1 88 09:31:00 106.81 223 Guide: PIROGOV Maksim 3 HOSCH Vivian GER B1 88 09:31:30 91.68 280 Guide: SCHILLINGER F 4 RUBANOVSKA Natalia UKR B2 99 09:32:00 70.17 85 Guide: NESTERENKO Lada 5 KLUG Clara GER B1 88 09:32:30 13.64 280 Guide: HARTL Martin 6 SHYSHKOVA Oksana UKR B2 99 09:33:00 0.00 90 Guide: KAZAKOV Vitaliy 7 LYSOVA Mikhalina (WL) NPA B2 99 09:33:30 0.00 500 Guide: IVANOV Alexey Men Middle,Visually Impaired 11 KANAFIN Kairat KAZ B2 99 09:40:30 204.91 Guide: ZHDANOVICH Anton 12 DUBOIS Thomas FRA B1 88 09:41:00 168.61 126 Guide: SAUVAGE Bastien 13 CHOI Bogue KOR B3 100 09:41:30 162.70 65 Guide: KIM Hyunwoo 14 UDALTSOV Vladimir NPA B3 100 09:42:00 150.03 137 Guide: BOGACHEV Ruslan 15 POVAROV Nikita NPA B3 100 09:42:30 149.93 206 Guide: ELISEEV Pavel 16 PONOMAREV Oleg NPA B2 99 09:43:00 137.80 32 Guide: ROMANOV Andrei 17 GARBOWSKI Piotr POL B3 100 09:43:30 135.49 69 Guide: TWARDOWSKI J 18 ARTEMOV Aleksandr NPA B1 88 09:44:00 125.38 209 Guide: CHEREPANOV Ilia 19 MAKHOTKIN Oleksandr UKR B3 100 09:44:30 124.74 16 Guide: NIKULIN Denys 20 HOLUB Yury BLR B3 100 09:45:00 82.45 45 Guide: BUDZILOVICH D 21 POLUKHIN Nikolai NPA B2 99 09:45:30 73.45 345 Guide: BEREZIN Eduard 22 CHALENCON Anthony FRA B1 88 09:46:00 22.36 133 Guide: VALVERDE Simon 23 LUK'YANENKO Vitaliy UKR B3 100 09:46:30