Towards TCP/IP for Wireless Sensor Networks

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

AMNESIA 33: How TCP/IP Stacks Breed Critical Vulnerabilities in Iot

AMNESIA:33 | RESEARCH REPORT How TCP/IP Stacks Breed Critical Vulnerabilities in IoT, OT and IT Devices Published by Forescout Research Labs Written by Daniel dos Santos, Stanislav Dashevskyi, Jos Wetzels and Amine Amri RESEARCH REPORT | AMNESIA:33 Contents 1. Executive summary 4 2. About Project Memoria 5 3. AMNESIA:33 – a security analysis of open source TCP/IP stacks 7 3.1. Why focus on open source TCP/IP stacks? 7 3.2. Which open source stacks, exactly? 7 3.3. 33 new findings 9 4. A comparison with similar studies 14 4.1. Which components are typically flawed? 16 4.2. What are the most common vulnerability types? 17 4.3. Common anti-patterns 22 4.4. What about exploitability? 29 4.5. What is the actual danger? 32 5. Estimating the reach of AMNESIA:33 34 5.1. Where you can see AMNESIA:33 – the modern supply chain 34 5.2. The challenge – identifying and patching affected devices 36 5.3. Facing the challenge – estimating numbers 37 5.3.1. How many vendors 39 5.3.2. What device types 39 5.3.3. How many device units 40 6. An attack scenario 41 6.1. Other possible attack scenarios 44 7. Effective IoT risk mitigation 45 8. Conclusion 46 FORESCOUT RESEARCH LABS RESEARCH REPORT | AMNESIA:33 A note on vulnerability disclosure We would like to thank the CERT Coordination Center, the ICS-CERT, the German Federal Office for Information Security (BSI) and the JPCERT Coordination Center for their help in coordinating the disclosure of the AMNESIA:33 vulnerabilities. -

An Open-Source, Extensible System for Laboratory Timing and Control Peter E

REVIEW OF SCIENTIFIC INSTRUMENTS 80, 115103 ͑2009͒ An open-source, extensible system for laboratory timing and control Peter E. Gaskell,a͒ Jeremy J. Thorn, Sequoia Alba, and Daniel A. Steck Department of Physics and Oregon Center for Optics, University of Oregon, Eugene, Oregon 97403-1274, USA ͑Received 16 July 2009; accepted 25 September 2009; published online 3 November 2009͒ We describe a simple system for timing and control, which provides control of analog, digital, and radio-frequency signals. Our system differs from most common laboratory setups in that it is open source, built from off-the-shelf components, synchronized to a common and accurate clock, and connected over an Ethernet network. A simple bus architecture facilitates creating new and specialized devices with only moderate experience in circuit design. Each device operates independently, requiring only an Ethernet network connection to the controlling computer, a clock signal, and a trigger signal. This makes the system highly robust and scalable. The devices can all be connected to a single external clock, allowing synchronous operation of a large number of devices for situations requiring precise timing of many parallel control and acquisition channels. Provided an accurate enough clock, these devices are capable of triggering events separated by one day with near-microsecond precision. We have achieved precisions of ϳ0.1 ppb ͑parts per 109͒ over 16 s. © 2009 American Institute of Physics. ͓doi:10.1063/1.3250825͔ I. INTRODUCTION ware must be run by a sufficiently primitive computer and the cost of upgrading the hardware to support modern inter- In a wide range of fields, including cold-atom physics, faces is prohibitive. -

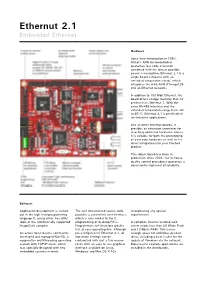

Ethernut 2.1 Embedded Ethernet

Ethernut 2.1 Embedded Ethernet Hardware Since their introduction in 1997, Atmel's AVR microcontrollers guarantee fast code execution combined with the lowest possible power consumption. Ethernut 2.1 is a single board computer with an extended temperature range, which integrates the 8-bit AVR ATmega128 into an Ethernet network. In addition to 100 Mbit Ethernet, the board offers a larger memory than its predecessor, Ethernut 1. With the extra RS-485 interface and the extended temperature range from -40 to 85°C, Ethernut 2.1 is predestined for industrial applications. Like all other Ethernut boards, it provides an extension connector for attaching additional hardware. Hence it is suitable for both the prototyping of your own hardware as well as for direct integration into your finished product. This robust board has been in production since 2003. Our in-house quality control procedures guarantee a consistently high level of reliability. Software Application development is carried The well documented source code incorporating any special out in the high level programming provides a convenient user interface, requirements. language C, using either free GNU which is very similar to the C tools or the commercially supported programming of desktop PC’s. A complete Internet enabled web ImageCraft compiler. Programmers will therefore quickly server needs less than 60 kByte Flash feel at ease operating this. Although and 12 kByte RAM. This leaves An active Open Source community pre-configured for Ethernut 2.1, all enough space for ambitious product developed and managed Nut/OS, a important settings can be ideas, including a boot loader for the cooperative multithreading operating customized with just a few mouse update of firmware via the network. -

Ethernut Software Manual Manual Revision: 2.4 Issue Date: November 2005

Ethernut Software Manual Manual Revision: 2.4 Issue date: November 2005 Copyright 2001-2005 by egnite Software GmbH. All rights reserved. egnite makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein. egnite products are not intended for use in medical, life saving or life sustaining applications. egnite retains the right to make changes to these specifications at any time, without notice. All product names referenced herein are trademarks of their respective companies. Ethernut is a registered trademark of egnite Software GmbH. Contents About Nut/OS and Nut/Net . .1 Nut/OS Features . .1 Nut/Net Features . .1 Quick Start with ICCAVR . .2 Installing ICCAVR . .2 Installing Nut/OS . .2 Configuring Nut/OS . .4 Configuring ImageCraft . .8 Creating the First Nut/OS Application . .11 Quick Start with AVR-GCC on Linux . .14 Installing AVR-GCC on Linux . .14 Installing Nut/OS . .14 Configuring Nut/OS . .14 Creating the First Nut/OS Application . .19 Quick Start with WinAVR . .22 Installing AVR-GCC on Windows . .22 Installing Nut/OS . .22 Configuring Nut/OS . .24 Creating the First Nut/OS Application . .27 Running the Embedded Webserver . .29 Nut/OS . .31 System Initialization . .31 Thread Management . .31 Timer Management . .32 Heap Management . .33 Event Management . .33 Stream I/O . .34 File System . .36 Device Drivers . .36 Nut/Net . .37 Network Device Initialization with DHCP . .37 Socket API . .38 Protocols . .40 Conversion Function . .41 Network Buffers . .41 Simple TCP Server . .43 Initializing the Ethernet Device . -

Ethernut Starter Kit Serial and Network I/O

§ Expandable device driver supports on-board Ethernut Starter Kit serial and network I/O. Easy application via stream I/O and TCP/UDP socket interface. § Several application examples for TCP/IP client/server communication including Telnet and Web Server. Contents of the Kit Hardware § Multilayer Ethernut Board, assembled and tested with preloaded software sample. § In-system programming adapter for the PC parallel printer port. § DB-9 serial cable for the PC com port. § Printed hardware manual including quick start guide. Software The included CDROM contains Description § Complete C and assembly source code with EthernutTM is a small (80 x 100 mm) board BSD type licence. Royality-free for open or combining Atmel's ATmega 128 RISC closed source commercial or non- Microcontroller with Realtek's RTL8019AS commercial application. Ethernet Controller. The board is well suited for § GNU C Compiler Tools for application a wide range of Internet enabled applications. It development. is ready to be plugged into a 10BaseT Ethernet § Additional manuals including detailed API network. documentation. Features Prerequisites for Operation Hardware § A standard Linux or Windows PC equipped § ATmega 128 RISC Microcontroller. with a twisted pair Ethernet Adapter Card. § Full duplex IEEE 802.3 compliant Ethernet § Unregulated power supply with AC 7-12V controller with on-board RJ-45 connector or DC 9-15V, 100 mA minimum, on a for twisted pair networks. standard 2.1 mm barrel connector. § RS-232 serial port with on-board DB-9 § 100/10Base-T or 10Base-T network or a connector for debugging or application twisted pair cross cable. usage. § 128 Kbyte in-system programmable flash ROM, 4 Kbyte in-system programmable Order EEPROM and 32 Kbyte SRAM. -

Running BSD-Licensed Software on BSD-Licensed Hardware

Running BSD-licensed Software on BSD-licensed Hardware Marius Strobl [email protected] EuroBSDcon 2012 Warsaw University of Technology Warsaw, Poland October 20 { 21, 2012 Embedded systems development typical requirements Microcontroller (µC) based reference design providing: I Analog/Digital Converters (ADCs) I General Purpose Input/Output (GPIO) interface I IEEE 802.3 [1] compliant Ethernet Media Access Controller (MAC) I Real-Time Clock (RTC) I Universal (Synchronous/)Asynchronous Receiver Transmitter (U(S)ART) for EIA RS-232-C [2] or RS-485 [3] I Internal or external volatile (RAM) and non-volatile (NVRAM) random-access memory, flash read-only memory (ROM) I IEEE 1149.1 [4] compliant Joint Test Action Group (JTAG) interface or Serial Peripheral Interface (SPI) for In-System Programming (ISP) and optionally debugging I Source code of real-time kernel plus drivers for above devices I Communication protocol stacks, mainly for Transmission Control Protocol [5]/Internet Protocol [6] (TCP/IP) 2 / 37 Ethernut board family of reference design boards Figure : Ethernut 1.3G [7] Figure : Ethernut 2.1B [8] Figure : Ethernut 3.1D [9] Figure : Ethernut 5.0F [10] 3 / 37 Ethernut board family features Model Microcontroller RAM Flash MAC [Bytes] [Bytes] [Mbps] Ethernut 1 AVR® 8-bit 4k int. 128k 10 ATmega128 32k ext. Ethernut 2 AVR® 8-bit 4k int. 128k 10/100 ATmega128 512k ext. Ethernut 3 ARM7-TDMI 32-bit 256k 4M 10/100 AT91R40008 Ethernut 5 ARM9 32-bit 32k int. 512k int. 10/100 AT91SAM9XE512 128M ext. 4M ext. 1G ext. Table : Microcontrollers and memory of the Ethernut board models 4 / 37 Ethernut board family features c'tinued Model ADC GPIO NVRAM I2C, RTC, UART/ [lines] [Bytes] MMC/SD slot USART Ethernut 1 8 chan. -

How Embedded TCP/IP Stacks Breed Critical Vulnerabilities

How Embedded TCP/IP Stacks Breed Critical Vulnerabilities Daniel dos Santos, Stanislav Dashevskyi, Jos Wetzels, Amine Amri FORESCOUT RESEARCH LABS #BHEU @BLACKHATEVENTS Who we are • Daniel dos Santos, Research Manager • Stanislav Dashevskyi, Security Researcher • Jos Wetzels, Security Researcher • Amine Amri, Security Researcher “At Forescout Research Labs we analyze the security implications of hyper connectivity and IT-OT convergence.” FORESCOUT RESEARCH LABS 2 #BHEU @BLACKHATEVENTS Outline • Project Memoria • AMNESIA:33 - vulnerabilities on open-source TCP/IP stacks • Analysis of TCP/IP stack vulnerabilities o Affected components o Vulnerability types & Anti-patterns o Exploitability & Impact • The consequences of TCP/IP stack vulnerabilities • Conclusion & what comes next FORESCOUT RESEARCH LABS 3 #BHEU @BLACKHATEVENTS Project Memoria FORESCOUT RESEARCH LABS 4 #BHEU @BLACKHATEVENTS Project Memoria • Goal: large study of embedded TCP/IP stack security o Why are they vulnerable? How are they vulnerable? What to do about it? o Quantitative and qualitative o Forescout Research Labs and other collaborations 1990s 2020 FORESCOUT RESEARCH LABS 5 #BHEU @BLACKHATEVENTS Embedded Systems Supply chain http://smartbox.jinr.ru/doc/chip-rtos/software.htm Applications / System Distributer / Components Devices Connectivity End User Services Integration Reseller • MCU • IP Cam • Cellular • Library • SoC • Router • LPWAN • Daemon • Modem • ECU • Wi-Fi • Platform FORESCOUT RESEARCH LABS 6 #BHEU @BLACKHATEVENTS Why target protocol stacks? • Wide deployment -

ARM Processors

Embedded Systems Dariusz Makowski Department of Microelectronics and Computer Science tel. 631 2720 [email protected] http://neo.dmcs.pl/sw Department of Microelectronics and Computer Science 1 Embedded Systems Input-Output ports of AMR processor based on ATMEL ARM AT91SAM9263 Department of Microelectronics and Computer Science 2 Embedded Systems Department of Microelectronics and Computer Science 3 Embedded Systems Documentation for AT91SAM9263 Microcontroller Department of Microelectronics and Computer Science 4 Embedded Systems Documentation for AT91SAM9263 – I/O Ports Źródło: ATMEL, doc6249.pdf, strona 425 Department of Microelectronics and Computer Science 5 Embedded Systems Block Diagram of 32-bits I/O Port Advanced Peripheral Bus Department of Microelectronics and Computer Science 6 Embedded Systems Power Consumption vs Clock Signal Department of Microelectronics and Computer Science 7 Embedded Systems Control Registers for I/O ports Department of Microelectronics and Computer Science 8 Embedded Systems Memory Map Department of Microelectronics and Computer Science 9 Embedded Systems Documentation as Source of Registers' Information Department of Microelectronics and Computer Science 10 Embedded Systems Simplified Block Diagram of I/O Port PIO_ODR = 1 Port I/O PIO_ODSR (Output Data Status Reg.) PIO_CODR (clear) R Q D Q PIO_OER PIO_OSR PIO_SODR (set) S Clk Clk PIO_OER – Output Enable Register PIO_ODR – Output Disable Register PIO_OSR – Output Status Register PIO_PDSR (Pin Data Status Register) Department of Microelectronics and Computer Science 11 Embedded Systems I/O Port – How to Control Output ? Output Enable Reg. Pull-Up Enable Reg. 100 k Periph. A status Reg. PIO Enable Reg. Multi-driver Enable Reg. (OpenDrain) Set Output Data Reg. Department of Microelectronics and Computer Science 12 Embedded Systems I/O – How to Read Input ? Pin Data Status Reg. -

Ethernut 1.3 Rev-G Hardware Manual

Ethernut Version 1.3 Hardware User`s Manual Manual Revision: 1.8 Issue date: November 2005 Copyright 2001-2005 by egnite Software GmbH. All rights reserved. egnite makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein. egnite products are not intended for use in medical, life saving or life sustaining applications. egnite retains the right to make changes to these specifications at any time, without notice. All product names referenced herein are trademarks of their respective companies. Ethernut is a registered trademark of egnite Software GmbH. Contents About the Ethernut 1.3 Board . .1 Ethernut Features . .1 Block Diagram . .2 LED Indicators . .3 Serial Ports . .3 Ethernet Port . .3 Expansion Port . .3 Power Supply . .4 Watchdog Timer . .4 System Clock . .4 Flash ROM . .4 Static RAM . .5 EEPROM . .5 Configuration Jumpers . .5 Upgrading from Previous Ethernut Revisions . .5 Quick Start . .6 Prerequisites for Operation . .6 Precautions . .6 Board Installation . .7 Testing the Board . .9 Ethernet Controller Read/Write Loop . .10 Jump to Bootloader . .10 SRAM Read/Write Loop . .10 Send Broadcasts Loop . .10 Exit BaseMon . .10 Network Configuration . .11 DHCP/BOOTP Method . .12 Fixed IP Address . .12 ARP Method . .12 Testing Network Operation . .13 Jumper Configuration . .14 Jumper Overview . .14 Hardware Expansion . .15 Expansion Port . .15 Analog Input Port . .16 Troubleshooting . .17 Sick Ethernuts . .20 Schematic . .21 About the Ethernut 1.3 Board About the Ethernut 1.3 Board Low-ccost Ethernet capability can be added to many embedded applications. -

University of Southern Queensland Faculty of Engineering & Surveying

University of Southern Queensland Faculty of Engineering & Surveying Embedded IP for Small Devices A dissertation submitted by Simon Neil Brown in fulfilment of the requirements of ENG4112 Research Project towards the degree of Bachelor of Engineering (Computer and Electronic) Submitted: October, 2005 Abstract Today technology utilising the Web is one of the most popular used computer technolo- gies. It would be hard to imagine any computer user whom does not have a web browser or used a web browser. A web browser can view web-pages developed or located within any operating systems, whether that is a Windows, Linux or even iMac workstation. The beauty of this technology is that the web client software (Web Browser) can com- municate with any web-server using the Hyper-text Transfer Protocol (HTTP). Also the pages displayed by these systems look identical even though they are generated by a variety of computer systems. With embedded systems in mind, it would be silly not to utilise this technology for control and monitoring purposes. However, currently small embedded devices, those that are classified with less than 10 kB of ROM, have limited IP connectivity. This is because the current implementations occupy more than the device possesses. The driver for this research project is the apparent lack of available IP implementations for small embedded devices. Typical embedded IP stacks range from 14kB up to and exceeding 500kB. For small devices, less than 10 kB, this puts this function out of reach. However, this project aims to implement a subset of Internet Protocols to provide a means of control and monitoring for a small embedded device. -

Ethernut 3.1 Hardware Manual Manual Revision: 3.0 Issue Date: November 2009 Copyright 2005-2009 Egnite Gmbh

Ethernut 3.1 Hardware Manual Manual Revision: 3.0 Issue date: November 2009 Copyright 2005-2009 egnite GmbH. All rights reserved. egnite makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document. Nor does it make a commitment to update the information contained herein. egnite products are not intended for use in medical, life saving or life sustaining applications. egnite retains the right to make changes to these specifications at any time, without notice. All product names referenced herein are trademarks of their respective companies. Ethernut is a registered trademark of egnite GmbH. Contents About the Ethernut 3.1 Board................................................................................5 Ethernut Features........................................................................................................5 Quick Start............................................................................................................6 Prerequisites for Operation...........................................................................................6 Precautions................................................................................................................6 Board Installation........................................................................................................7 Using the Boot Loader............................................................................................8 TFTP Server...............................................................................................................9 -

Ethernut Software Manual Manual Revision: 2.0 Issue Date: September 2004

Ethernut Software Manual Manual Revision: 2.0 Issue date: September 2004 Copyright 2001-2004 by egnite Software GmbH. All rights reserved. egnite makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein. egnite products are not intended for use in medical, life saving or life sustaining applications. egnite retains the right to make changes to these specifications at any time, without notice. All product names referenced herein are trademarks of their respective companies. Ethernut is a registered trademark of egnite Software GmbH. Contents About Nut/OS and Nut/Net . .1 Nut/OS Features . .1 Nut/Net Features . .1 Quick Start with ICCAVR . .2 Installing ICCAVR . .2 Installing Nut/OS . .2 Configuring Nut/OS . .2 Configuring ImageCraft . .6 Creating the First Nut/OS Application . .9 Quick Start with AVR-GCC on Linux . .12 Installing AVR-GCC on Linux . .12 Installing Nut/OS . .12 Configuring Nut/OS . .12 Creating the First Nut/OS Application . .17 Quick Start with WinAVR . .19 Installing AVR-GCC on Windows . .19 Installing Nut/OS . .19 Configuring Nut/OS . .19 Creating the First Nut/OS Application . .23 Running the Embedded Webserver . .25 Nut/OS . .27 System Initialization . .27 Thread Management . .27 Timer Management . .28 Heap Management . .29 Stream I/O . .30 File System . .31 Device Drivers . .32 Nut/Net . .33 Network Device Initialization with DHCP . .33 Socket API . .34 Protocols . .36 Conversion Function . .37 Network Buffers . .37 Simple TCP Server . .39 Initializing the Ethernet Device .