Research Project to Study Cadmium Selenide (Cdse) Solar Cells

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Zinc Selenide Quantum Dots

Chapter 3 Zinc Selenide Quantum Dots 3.1 Introduction: Nanoscale materials have been extensively studied in recent years to study the evolution of the electronic structure from molecules to bulk. The properties or the electronic structure of nanoparticles is not a simple extrapolation of its corresponding molecular or bulk state. Quantum dots show unique features arising from the variation in crystal structure parameters, discretization of electron energy levels, concentration of oscillator strength for particular transitions, high polarizability of electron energy levels and increased surface to volume ratio [1-4]. Quantum confinement in semiconductors leads to discrete transitions that are blue shifted in energy from the bulk. Inhomogeneous broadening of the optical spectra due to size distribution and shape variations of the nanoparticles, conceal the fine structure in the energy states of quantum dots. In order to study the evolution of the electronic, optical and structural properties of material with size it is essential to synthesize nanoparticles of different sizes (with narrow size distribution) and controlled surface properties. II-VI semiconductors are relatively easy to synthesize, yielding free standing colloidal quantum dots by wet chemical routes. The evolving electronic structure as a function of size can be determined by non-contact optical probes in case of direct band gap II-VI semiconductors. The quantum size effects in CdSe nanoparticles with wurtzite structure are thoroughly investigated [5], while relatively less attention is being paid to other II-VI nanocrystals such as zinc selenide or zinc oxide. ZnSe is a II-VI direct band gap, zinc blende semiconductor with a bulk band gap of 2.7 eV at room temperature. -

Selenium Nutritional, Toxicologic, and Clinical Aspects ANNA M

160 Articles Selenium Nutritional, Toxicologic, and Clinical Aspects ANNA M. FAN, PhD, Berkeley, and KENNETH W. KIZER, MD, MPH, Sacramento, California This is one ofa series ofarticles from western state public health departments. Despite the recent findings ofenvironmental contamination, selenium toxicosis in humans is exceedingly rare in the United States, with the few known cases resulting from industrial accidents and an episode involving the ingestion of superpotent selenium supplements. Chronic selenosis is essentially unheard of in this country because of the typical diversity of the American diet. Nonetheless, because ofthe growing public interest in selenium as a dietary supplement and the occurrence ofenvironmental selenium contamination, medical practitioners should be familiar with the nutritional, toxicologic, and clinical aspects of this trace element. (Fan AM, Kizer KW: Selenium-Nutritional, toxicologic, and clinical aspects. West J Med 1990 Aug; 153:160-167) Since the recognition of the nutritional essentiality of and other parts of the world.4 Highly seleniferous soils selenium (Se) in animals in 1957, there has been ever- yielding selenium-toxic plants (such as Astragalus bisulca- increasing interest in this trace element. This interest has tus) are widespread in South Dakota, Wyoming, Montana, heightened in the past decade concomitant with the recog- North Dakota, Nebraska, Kansas, Colorado, Utah, Arizona, nition of selenium's essential nutritional role in humans and New Mexico. Soil containing high selenium concentra- and reports of selenium toxicity among humans. Interest in tions but not yielding toxic plants is found in Hawaii. selenium has been further aroused recently by the findings of elevated levels of this compound in certain soils and wa- Chemical Forms ter sources in the western United States, leading to adverse Selenium is a nonmetallic element chemically related to effects on fish and wildlife (T. -

The Electronic and Optical Properties of Close Packed Cadmium Selenide Quantum Dot Solids

The Electronic and Optical Properties of Close Packed Cadmium Selenide Quantum Dot Solids by Cherie Renee Kagan B. S. E. Materials Science and Engineering B. A. Mathematics University of Pennsylvania, Philadelphia, PA 1991 Submitted to the Department of Materials Science and Engineering in Partial Fulfillment of the Requirements for the Degree of DOCTOR OF PHILOSOPHY at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY September 1996 0 1996 Massachusetts Institute of Technology All rights reserved Signature of the Author Departmenf of Materials Science and Engineering August 9, 1996 Certified by_ Moungi G. Bawendi Professor of Chemistry Thesis Supervisor Accepted by Linn W. Hobbs John F. Elliott Professor of Materials Science and Engineering Chair, Department Committee on Graduate Students AROHIvES ()F Tac(.!-otodY SEP 2 71996 Room 14-0551 77 Massachusetts Avenue Cambridge, MA 02139 Ph: 617.253.2800 MITLbries Email: [email protected] Document Services http://Iibraries.mit.eduldocs DISCLAIMER OF QUALITY Due to the condition of the original material, there are unavoidable flaws in this reproduction. We have made every effort possible to provide you with the best copy available. If you are dissatisfied with this product and find it unusable, please contact Document Services as soon as possible. Thank you. The images contained in this document are of the best quality available. 2 3 The Electronic and Optical Properties of Close Packed Cadmium Selenide Quantum Dot Solids by Cherie Renee Kagan - Submitted to the Department of Materials Science and Engineering on August 9, 1996 in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Materials Science and Engineering Abstract The synthesis, structural characterization, optical spectroscopy, and electronic characterization of close packed solids prepared from CdSe QD samples tunable in size from 17 to 150 A in diameter (a<4.5%) are presented. -

Zinc Selenide Optical Crystal

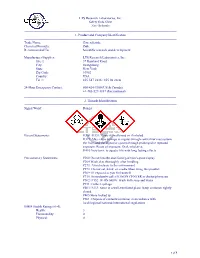

Revision date: 07/12/2020 Revision: 1 SAFETY DATA SHEET Zinc Selenide Optical Crystal SECTION 1: Identification of the substance/mixture and of the company/undertaking 1.1. Product identifier Product name Zinc Selenide Optical Crystal CAS number 1315-09-9 EU index number 034-002-00-8 EC number 215-259-7 1.2. Relevant identified uses of the substance or mixture and uses advised against Identified uses Optical Material for manufacture of Optical Components 1.3. Details of the supplier of the safety data sheet Supplier Knight Optical (UK) LTD Roebuck Business Park Harrietsham Kent ME17 1AB UK +44 (0)1622 859444 [email protected] 1.4. Emergency telephone number Emergency telephone +44 (0)1622 859444 (Monday to Friday 08:30 to 17:00 GMT) SECTION 2: Hazards identification 2.1. Classification of the substance or mixture Classification (EC 1272/2008) Physical hazards Not Classified Health hazards Acute Tox. 3 - H301 Acute Tox. 3 - H331 Environmental hazards Aquatic Chronic 1 - H410 2.2. Label elements EC number 215-259-7 Hazard pictograms Signal word Danger Hazard statements H301+H331 Toxic if swallowed or if inhaled. H410 Very toxic to aquatic life with long lasting effects. 1/10 Revision date: 07/12/2020 Revision: 1 Zinc Selenide Optical Crystal Precautionary statements P264 Wash contaminated skin thoroughly after handling. P270 Do not eat, drink or smoke when using this product. P273 Avoid release to the environment. P403+P233 Store in a well-ventilated place. Keep container tightly closed. P501 Dispose of contents/ container in accordance with national regulations. -

Table of Contents (Print, Part 1)

CONTENTS - Continued PHYSICAL REVIEW B THIRD SERIES, VOLUME 90, NUMBER 16 OCTOBER 2014-15(II) COMMENTS Comment on “Canonical magnetic insulators with isotropic magnetoelectric coupling” (3 pages) ............... 167101 J. M. Perez-Mato, Samuel V. Gallego, E. S. Tasci, L. Elcoro, and M. I. Aroyo Reply to “Comment on ‘Canonical magnetic insulators with isotropic magnetoelectric coupling’ ” (1 page) . 167102 Sinisa Coh and David Vanderbilt Comment on “Ideal strength and phonon instability in single-layer MoS2” (3 pages) .......................... 167401 Ryan C. Cooper, Jeffrey W. Kysar, and Chris A. Marianetti Reply to “Comment on ‘Ideal strength and phonon instability in single-layer MoS2’”(3 pages) ................ 167402 Tianshu Li The editors and referees of PRB find these papers to be of particular interest, importance, or clarity. Please see our Announcement Phys. Rev. B 77, 130001 (2008). CONTENTS - Continued PHYSICAL REVIEW B THIRD SERIES, VOLUME 90, NUMBER 16 OCTOBER 2014-15(II) Readout and dynamics of a qubit built on three quantum dots (12 pages) .................................... 165427 Jakub Łuczak and Bogdan R. Bułka Experimental verification of reciprocity relations in quantum thermoelectric transport (6 pages) ................ 165428 J. Matthews, F. Battista, D. Sanchez,´ P. Samuelsson, and H. Linke Noncollinear magnetic phases and edge states in graphene quantum Hall bars (5 pages) ....................... 165429 J. L. Lado and J. Fernandez-Rossier´ Roton-maxon spectrum and instability for weakly interacting dipolar excitons in a semiconductor layer (9 pages) 165430 A. K. Fedorov, I. L. Kurbakov, and Yu. E. Lozovik Influence of edge and field effects on topological states of germanene nanoribbons from self-consistent calculations (7 pages) ................................................................................ 165431 Lars Matthes and Friedhelm Bechstedt Electronic structure and magnetic properties of cobalt intercalated in graphene on Ir(111) (10 pages) .......... -

Material Safety Data Sheet

LTS Research Laboratories, Inc. Safety Data Sheet Zinc Selenide ––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––– 1. Product and Company Identification ––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––– Trade Name: Zinc selenide Chemical Formula: ZnSe Recommended Use: Scientific research and development Manufacturer/Supplier: LTS Research Laboratories, Inc. Street: 37 Ramland Road City: Orangeburg State: New York Zip Code: 10962 Country: USA Tel #: 855-587-2436 / 855-lts-chem 24-Hour Emergency Contact: 800-424-9300 (US & Canada) +1-703-527-3887 (International) ––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––– 2. Hazards Identification ––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––– Signal Word: Danger Hazard Statements: H301+H331: Toxic if swallowed or if inhaled H373: May cause damage to organs through central nervous system, the liver, and the digestive system through prolonged or repeated exposure. Route of exposure: Oral, inhalative. H410 Very toxic to aquatic life with long lasting effects Precautionary Statements: P260 Do not breathe dust/fume/gas/mist/vapours/spray P264 Wash skin thoroughly after handling P273: Avoid release to the environment P270: Do not eat, drink, or smoke when using this product. P309: IF exposed or you feel unwell: P310: Immediately call a POISON CENTER or doctor/physician P302+P352: IF ON SKIN: Wash with soap and water P391: Collect -

Investigations of Phonons in Zinc Blende and Wurtzite by Raman Spectroscopy 25

ProvisionalChapter chapter 2 Investigations of of Phonons Phonons in Zinc in Zinc Blende Blende and Wurtziteand Wurtzite by Raman Spectroscopy by Raman Spectroscopy Lin Sun, Lingcong Shi and Chunrui Wang Lin Sun, Lingcong Shi and Chunrui Wang Additional information is available at the end of the chapter Additional information is available at the end of the chapter http://dx.doi.org/10.5772/64194 Abstract The importance of phonons and their interactions in bulk materials is well known to those working in the fields of solid‐state physics, solid‐state electronics, optoelectronics, heat transport, quantum electronic, and superconductivity. Phonons in nanostructures may act as a guide to research on dimensionally confined phonons and lead to phonon effects in nanostructures and phonon engineering. In this chapter, we introduce phonons in zinc blende and wurtzite nanocrystals. First, the basic structure of zinc blende and wurtzite is described. Then, phase transformation between zinc blende and wurtzite is presented. The linear chain model of a one‐dimensional diatomic crystal and macroscopic models are also discussed. Basic properties of phonons in wurtzite structure will be considered as well as Raman mode in zinc blende and wurtzite structure. Finally, phonons in ZnSe, Ge, SnS2, MoS2, and Cu2ZnSnS4 nanocrystals are discussed on the basis of the above theory. Keywords: phonons, zinc blende, wurtzite, Raman spectroscopy, molecular vibration 1. Zinc blende and wurtzite structure Crystals with cubic/hexagonal structure are of major importance in the fields of electronics and optoelectronics. Zinc blende is typical face‐centered cubic structure, such as Si, Ge, GaAs, and ZnSe. Wurtzite is typical hexagonal close packed structure, such as GaN and ZnSe. -

Synthesis, Characterization and Optical Properties of Znse Nanoparticles

International Journal of Applied Engineering Research ISSN 0973-4562 Volume 13, Number 6 (2018) pp. 4606-4609 © Research India Publications. http://www.ripublication.com Synthesis, Characterization and Optical Properties of ZnSe Nanoparticles Anil Yadav1, 2*, S. P. Nehra2, Dinesh Patidar3 1Department of Chemical Engineering, Deenbandhu Chhotu Ram University of Science & Technology, Murthal, Sonepat (Haryana) India. 2Centre of Excellence for Energy & Environmental Studies, Deenbandhu Chhotu Ram University of Science & Technology, Murthal, Sonepat (Haryana) India. 3Department of Physics, Seth G.B. Podar College, Nawalgarh, Jhunjhunu (Rajasthan) India. *Corresponding Author Abstract characterization of ZnSe semiconductors consisting particles of 2-100 nm, which are generally referred as quantum dots The chemical co-precipitation method was employed to and nanocrystals. The interests of the researchers are mainly synthesize zinc selenide (ZnSe ) nanoparticles with the help of because of their size-tunable optical, electronic and chemical Selenium powder, sodium borohydride, zinc acetate. properties [3,4]. Further miniaturization of optical and Mercaptoethanol was added as capping agent. The XRD, electronic devices leads to their commercial applications [1,4- SEM and TEM techniques were employed for the 9] are as diverse as solar cells, catalysis, biological labelling, characterization of ZnSe nanoparticles. The average diameter light-emitting diodes. As we know that Size and shape of the of ZnSe nanoparticles is 15 nm. HR transmission electron nanomaterials are responsible for their properties but synthesis microscopy (HRTEM) image displays the crystalline features of stable monodispersed nanocrystals is still a great challenge of ZnSe nanoparticles. The PL emission spectrum indicates a in Nanoscience. The control of shape of nanocrystals is also peak centered at 480 nm along with two shoulders at 453 and very important .The correlation exists between the shape and 520 nm. -

Solid State Recrystallization of II-VI Semiconductors : Application to Cadmium Telluride, Cadmium Selenide and Zinc Selenide R

Solid State Recrystallization of II-VI Semiconductors : Application to Cadmium Telluride, Cadmium Selenide and Zinc Selenide R. Triboulet, J. Ndap, A. El Mokri, A. Tromson Carli, A. Zozime To cite this version: R. Triboulet, J. Ndap, A. El Mokri, A. Tromson Carli, A. Zozime. Solid State Recrystallization of II-VI Semiconductors : Application to Cadmium Telluride, Cadmium Selenide and Zinc Selenide. J. Phys. IV, 1995, 05 (C3), pp.C3-141-C3-149. 10.1051/jp4:1995312. jpa-00253678 HAL Id: jpa-00253678 https://hal.archives-ouvertes.fr/jpa-00253678 Submitted on 1 Jan 1995 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. JOURNAL DE PHYSIQUE IV Colloque C3, supplCment au Journal de Physique 111, Volume 5, avril 1995 Solid State Recrystallization of 11-VI Semiconductors: Application to Cadmium Telluride, Cadmium Selenide and Zinc Selenide R. Triboulet, 3.0. Ndap, A. El Mokri, A. Tromson Carli and A. Zozime CNRS, Laboratoire de Physique des Solides de Bellevue, 1 place Aristide Briand, F 92195 Meudon cedex, France Abstract : Solid state recrystallization (SSR) has been very rarely used for semiconductors. It has nevertheless been proposed, and industrially used, for the single crystal growth of cadmium mercury telluride according to a quench-anneal process. -

Chalcogenide Glasses for Infrared Applications: New Synthesis Routes and Rare Earth Doping

Chalcogenide Glasses for Infrared Applications: New Synthesis Routes and Rare Earth Doping Item Type text; Electronic Dissertation Authors Hubert, Mathieu Publisher The University of Arizona. Rights Copyright © is held by the author. Digital access to this material is made possible by the University Libraries, University of Arizona. Further transmission, reproduction or presentation (such as public display or performance) of protected items is prohibited except with permission of the author. Download date 27/09/2021 06:13:56 Link to Item http://hdl.handle.net/10150/223357 CHALCOGENIDE GLASSES FOR INFRARED APPLICATIONS: NEW SYNTHESIS ROUTES AND RARE EARTH DOPING By Mathieu Hubert __________________________________ A Dissertation Submitted to the Faculty of the DEPARTMENT OF MATERIALS SCIENCE AND ENGINEERING In Partial Fulfillment of the Requirements For the Degree of DOCTOR OF PHILOSOPHY In the Graduate College THE UNIVERSITY OF ARIZONA 2012 2 THE UNIVERSITY OF ARIZONA GRADUATE COLLEGE As members of the Dissertation Committee, we certify that we have read the dissertation prepared by Mathieu Hubert entitled Chalcogenide glasses for infrared applications: new synthesis routes and rare earth doping and recommend that it be accepted as fulfilling the dissertation requirement for the Degree of Doctor of Philosophy _______________________________________________________________________ Date: 03/30/2012 Pierre Lucas _______________________________________________________________________ Date: 03/30/2012 B.G. Potter _______________________________________________________________________ -

Effect of Thickness on the Opticalproperties of Zinc Selenide Thin Films

Journal of Non-Oxide Glasses Vol. 3, No 3, 2011, p. 105 - 111 EFFECT OF THICKNESS ON THE OPTICALPROPERTIES OF ZINC SELENIDE THIN FILMS N.A. OKEREKE*, I.A. EZENWA2 AND A.J. EKPUNOBIa Department Of Industrial Physics, Anambra State University,Uli, Anambra State. aDepartment Of Physics And Industrial Physics, Nnamdi Azikiwe University, Awka, Anambra State. The zinc selenide (ZnSe) thin films of thicknesses 1.60µm and 1.64µm were chemically deposited on well cleaned glass substrate at room temperature. The films are polycrystalline with cubic structure, confirmed by x-ray diffractogram. The optical spectra of zinc selenide thin films were recorded in the wavelength range of 0.36µm and 1.10µm. The spectral absorption data shows that the films absorb in the ultra violet range of 0.36- 0.45 microns and have almost zero absorbance in VIS-IR regions of the spectrum. The films have average index of refraction of 2.0. The plot of α² versus h showed a direct band gap range of 2.70eV-2.75eV. The band gap is found to decrease with increase in film thickness. (Recieved October 19, 2011; accepted September 23, 2011) Keyword: Semiconductor, thin film, Zinc selenide, chemical bath, characterization, application. 1. Introduction The 11-VI semiconductor compounds are important optoelectronics, luminescent and laser materials. Intensive research has been performed in the past to study the fabrication and characterization of these compounds in the form of thin films. Zinc selenide is a widely used 11-VI semiconductor. It is one of the most interesting binary wide band gaps of about 2.7eV at room temperature. -

Design and Characterization of a Process for Bulk Synthesis of Cadmium Selenide Quantum Dots

CALIFORNIA POLYTECHNIC STATE UNIVERSITY OF SAN LUIS OBISPO Design and Characterization of a Process for Bulk Synthesis of Cadmium Selenide Quantum Dots Susan Harada Materials Engineering Department California Polytechnic State University Advisor Dr. Richard Savage June 2, 2011 Approval Page Project Title: Design and Characterization of a Process for Bulk Synthesis of Cadmium Selenide Quantum Dots Author: Susan Harada Date Submitted: June 2, 2011 CAL POLY STATE UNIVERSITY Materials Engineering Department Since this project is a result of a class assignment, it has been graded and accepted as fulfillment of the course requirements. Acceptance does not imply technical accuracy or reliability. Any use of information in this report is done at the risk of the user. These risks may include catastrophic failure of the device or infringement of patent or copyright laws. The students, faculty, and staff of Cal Poly State University, San Luis Obispo cannot be held liable for any misuse of the project. Prof. Richard Savage ____________________________ Faculty Advisor Signature Prof. Trevor Harding ____________________________ Department Chair Signature ii Acknowledgements I would like to thank the following people for their help during my senior project: Dr. Richard Savage for guidance and support Dr. Philip Costanzo for expertise and insight Josh Angell for helping out all the time Boeing for project funding General LED for project funding iii Table of Contents Acknowledgements .....................................................................................................................................