A Real-Time Embedded Data Acquisition System For

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

LAB-Manual Iot for Intel Edison

Evaluation of Intel Architecture An Experimental Manual for Computer Architecture, Advanced Microprocessor, System On Chip (SoC) and Compiler Design In association with Intel Collaboration Program Designed by: Zeenat Shareef, MTech (Mobile and Pervasive Computing) Under the guidance of: Dr. S.R.N Reddy, HOD and Associate Professor, CSE Mr. Naveen , Mr. Sumit Verma, Intel Department of Computer Science Indira Gandhi Delhi Technical University for Women Kashmere Gate, Delhi-110006 LIST OF EXPERIMENTS EXP. No Description of Experiment 1. To familiarize with Intel Edison. 2. Write the steps to install the drivers and IDE for Intel Edison 3. Write the steps to configure Intel Edison and enable the WIFI module 4. To enable the Bluetooth module in Intel Edison and connect with a device. 5. Write the steps to blink the LED on the Intel Edison using Eclipse CDT remote explorer(WiFi). EXPERIMENT 1 AIM: To familiarize with Intel Edison. INTEL EDISON- A SOC based on Intel Atom The Intel Edison compute module is designed to lower the barriers to entry for anyone prototyping and producing IoT and wearable computing products. Intel Edison contains the core system processing and connectivity elements: processor, PMIC, RAM, eMMC, and Wi- Fi/BT. Intel Edison is a module that interfaces with end-user systems via a 70-pin connector. The Intel Edison compute module does not include any video input or output interfaces (MIPI CSI, MIPI DSI, HDMI, etc.). Internal image processing and graphics processing cores are disabled (ISP, PowerVR, VED, VEC, VSP, etc.). Intel Edison relies on the end-user support of input power. -

Intel Edison Workshop

Note: This presentation was made and provided by Intel during the Intel Embedded Education & Research Summit in March 2015 Intel Edison Workshop Setting up Edison Step by Step Our Workshop Goal: 1.Unbox Edison 2.Learn how to connect and configure Edison board: Serial connecton Name /WiFi set up/Password 3. Install drivers (New Windows Installer amd manual install) 4. Intel Development IoT Kit 5. Install IDEs 6. Run example code Intel® Edison Arduino Expansion Board Assembly https://software.intel.com/en‐us/articles/intel‐edison‐arduino‐expansion‐board‐assembly Microswitch and USB Ports Details The slider switches between USB host mode and USB device mode. Device mode: The switch is toggled down and a micro‐USB cable can be used to turn the Intel® Edison into a computer peripheral. Device mode allows you to do such things as: program the board over USB, or mount the onboard flash memory like a disk drive. Host mode: The switch is toggled up and USB peripherals with a standard‐sized USB cable (such as mice, keyboards, etc) can be plugged into the Intel® Edison. USB host mode requires the use of an external power adapter. The Intel Edison board has three USB ports: The middle port (Micro A type) is used for the following: •Power through USB •Ethernet over USB •Uploading Arduino sketches •Updating the firmware by using the board as a storage device, like a flash drive The edge port (Micro A type) is used to create a terminal connection by serial over USB only. Power Through DC Plug If you are going to use more power intensive features such as Wi‐Fi, a servo motor, or an Arduino shield, use a DC power supply in addition to the device mode micro‐USB cable. -

Intel® Desktop Board D33217GKE

Intel® Desktop Board D33217GKE Next Unit of Computing by Intel® • Superior processing and graphics • Stunningly small form factor • Advanced Technologies producT brief Next Unit of Computing by Intel® with Intel® Desktop Board D33217GKE 4” (10 cm) Think you know what small can do? Think again. No more compromising between performance, profile, and price. The Next Unit of Computing (NUC) is a tiny 4”×4”×2” computing device with the power of the 3rd generation Intel® Core™ i3 processor. Its lower power consumption enables innovative system designs and energy- efficient applications in places like digital signage, home entertainment, and portable uses. Superior processing and graphics Visibly smart graphics using the 3rd generation Intel® Core™ i3-3217U processor deliver amaz- ing performance and visually stunning graphics. Stunningly small form factor The 4”×4”×2” form factor unlocks a world of potential design applications, from digital signage and kiosks to portable innovations. 4” (10 cm) Advanced Technologies The NUC features two SO-DIMM sockets for expandability upto 16 GB of memory, two PCIe* mini-card connectors for flexible support of wireless and SSD configurations, BIOS vault tech- nology, fast boot and the Intel® Visual BIOS. The NUC also supports Intel® Anti-Theft™ Technol- ogy providing hardware intelligence designed to protect your device and its data if its lost or stolen. Intel® Core™ i3-3217U Processor Intel® QS77 Express Chipset 2 Intel® Desktop Board D33217GKE Features and Benefits 1 × USB 2.0 connector on the front panel -

Draft NISTIR 8320A, Hardware-Enabled Security

NISTIR 8320A Hardware-Enabled Security: Container Platform Security Prototype Michael Bartock Murugiah Souppaya Jerry Wheeler Tim Knoll Uttam Shetty Ryan Savino Joseprabu Inbaraj Stefano Righi Karen Scarfone This publication is available free of charge from: https://doi.org/10.6028/NIST.IR.8320A NISTIR 8320A Hardware-Enabled Security: Container Platform Security Prototype Michael Bartock Joseprabu Inbaraj Murugiah Souppaya Stefano Righi Computer Security Division AMI Information Technology Laboratory Atlanta, GA Jerry Wheeler Karen Scarfone Tim Knoll Scarfone Cybersecurity Uttam Shetty Clifton, VA Ryan Savino Intel Corporation Santa Clara, CA This publication is available free of charge from: https://doi.org/10.6028/NIST.IR.8320A June 2021 U.S. Department of Commerce Gina Raimondo, Secretary National Institute of Standards and Technology James K. Olthoff, Performing the Non-Exclusive Functions and Duties of the Under Secretary of Commerce for Standards and Technology & Director, National Institute of Standards and Technology National Institute of Standards and Technology Interagency or Internal Report 8320A 48 pages (June 2021) This publication is available free of charge from: https://doi.org/10.6028/NIST.IR.8320A Certain commercial entities, equipment, or materials may be identified in this document in order to describe an experimental procedure or concept adequately. Such identification is not intended to imply recommendation or endorsement by NIST, nor is it intended to imply that the entities, materials, or equipment are necessarily the best available for the purpose. There may be references in this publication to other publications currently under development by NIST in accordance with its assigned statutory responsibilities. The information in this publication, including concepts and methodologies, may be used by federal agencies even before the completion of such companion publications. -

Cisco Enterprise Wireless

Cisco Enterprise Wireless Intuitive Wi-Fi starts here 2nd edition Preface 7 Authors 8 Acknowledgments 10 Organization of this book 11 Intended audience 12 Book writing methodology 13 What is new in this edition of the book? 14 Introduction 15 Intent-based networking 16 Introducing Cisco IOS® XE for Cisco Catalyst® wireless 18 Benefits of Cisco IOS XE 19 Cisco wireless portfolio 22 Infrastructure components 29 Introduction 30 Deployment mode flexibility 32 Resiliency in wireless networks 41 Wireless network automation 58 Programmability 61 Radio excellence 63 Introduction 64 802.11ax/Wi-Fi 6 66 High density experience (HDX) 71 Hardware innovations 77 Introduction 78 Dual 5 GHz radio 79 Modularity 83 Multigigabit 85 CleanAir-SAgE 87 RF ASIC - software defined radio 89 Innovative AP deployment solutions 91 Infrastructure security 97 Introduction 98 Securing the network 100 Securing the air 109 Encrypted Traffic Analytics (ETA) 114 WPA3 119 Policy 121 Introduction 122 Security policy 123 QoS policy 132 Analytics 145 Introduction 146 Enhanced experience through partnerships 148 Cisco DNA Center – wireless assurance 150 Cisco location technology explained 156 Cisco DNA Spaces 160 Migrating to Catalyst 9800 163 The Catalyst 9800 configuration model 164 Configuration conversion tools 168 Inter-Release Controller Mobility (IRCM) 171 Summary 175 The next generation of wireless 176 References 177 Acronyms 178 Further reading 183 Preface 8 Preface Authors In May 2018, a group of engineers from diverse backgrounds and geographies gathered together in San Jose, California in an intense week-long collaborative effort to write about their common passion, enterprise wireless networks. This book is a result of that effort. -

Paper Title (Use Style: Paper Title)

Overview of architectures with Arduino boards as building blocks for data acquisition and control systems Vladimir Cvjetkovic Milan Matijevic Faculty of Science Faculty of Engineering University of Kragujevac University of Kragujevac Kragujevac, Serbia Kragujevac, Serbia [email protected] [email protected] Abstract— Standard SBCs (Single Board Computer) with Control of some local system number of standard shields and sensors can be used as building blocks for rapid development of network of intelligent devices with Upload of acquired and processed data to some cloud sensing, control and Internet access. Arduino family of boards network storage having high popularity and large number of sold units featuring Some or all of these functionalities can be present including open access, reliability, robustness, standard connections and low prices, possesses large potential for implementation of also some specific not mentioned here. Mentioned autonomous remote measurement and control systems of various functionalities are quite general and do not pose limitations by levels of complexity. As Arduino boards can function themselves, as the real limits of IoT devices are mainly independently, they are complete small computer platforms that determined by processing power, speed, available memory, can perform various tasks requiring some kind of interaction with power consumption and similar characteristics. If the task for the outer world. Arduino boards can be used and programmed in some IoT device is too demanding, the possibility of logically various ways, and can be arranged in various combinations redefining the task so that more than one IoT device could be forming some typical implementation architectures that this paper used and combined to fulfill the given task, should be discusses. -

An Open Source Tool for Iot Development What Is the Product

An Open Source Tool for IoT Development What is the product 2 The technology: Hardware ▪ Before Raspberry Pi Currently experiencing rapid growth 7,000 ▪ expensive embedded devices 6,000 ▪ few devices 5,000 4,000 ▪ Raspberry Pi changed 3,000 the game 2,000 1,000 0 2014 2015 2016 Number of connected devices (millions) 3 Our journey: The vision ▪ Goal: ▪ A new approach towards engineering ▪ IoT accessible to everyone Create, modify, tweak, customize current solutions to your needs and use cases 4 The IoT stack The problem • Arduino (Uno) does well on Level 2 but does not follow the upper stack • Raspberry Pi follows the full stack, but lacks the benefits of Arduino 5 Microcontrollers vs Embedded Boards ▪ Arduino Yun preferred to Raspberry Pi ▪ The fault ▪ development tools ▪ accessibility Most of the projects are not IoT projects, they fall into electronics or programming 6 The solution ▪ Transfer the accessibility typical of Arduino to Raspberry Pi Ease to use Direct access High Use from productivity anywhere 7 Our tools for IoT : Wyliodrin ▪ Since 2013 ▪ Fully Web-based ▪ Complex IDE ▪ Open Source components ▪ Free for basic use ▪ Supports various hardware: Arduino Yun, Raspberry Pi, Intel® Galileo, Intel® Edison, UDOO, BeagleBone Black 8 Wyliodrin STUDIO ▪ Open Source ▪ Available for ▪ Arduino Yun ▪ UDOO Neo ▪ Raspberry Pi ▪ BeagleBone Black ▪ Works locally 9 Wyliodrin STUDIO Library manager Ethernet / WiFi Run project connection manager Project Manager Connected board Task manager Code Close board connection Show / hide console Board -

Content Creation Solution Brief

Content Creation Solution Brief Intel® NUC delivers stunning visuals and edge-of-your-seat performance in an ultra-small package. Powered by a visibly smart 3rd generation Intel® Core™ i5 processor on a 4-by-4 inch board and enclosed in a tiny case, the Intel NUC is big on performance yet surprisingly small in size. It’s an ideal form factor that can be easily transported to the studio, while packing the horsepower to record, mix, create, and play back amazing audio and video content. Intel NUC is the definitive crowd-pleaser for today’s prosumer. B007 Multiscreen Content Creaton Setup Technologies This section offers a guideline for the hardware and software needed to design Intel NUC into a small form factor prosumer solution. Included in Intel NUC Kit: • Intel NUC – DC53427HYE • VESA Bracket • Power Adapter Hardware Needed Quantity Item Manufacturer Model 1 Intel® NUC DC53427HYE Intel® Intel® Next Unit of Computing Kit DC53427HYE 2 Memory Any 4 GB DDR3 1600 SODIMM 1 Storage Intel Intel® Solid-State Drive 525 Series 240 GB mSATA 1 Intel® Centrino Wireless Intel Intel Centrino 6235 IEEE 802.11n Mini PCI Express* Bluetooth* 4.0 - Wi-Fi/Bluetooth Combo Adapter 2 Display Port Capable Displays Any Any 1 HDMI Capable Display Any Any 1 USB Audio Interface Any Any 2 Reference Monitor Speakers Any Any 1 External Storage Any Any USB or Network Attached Storage Software Needed Item Manufacturer Model Pro Tools* Avid® Technology, Inc. http://www.avid.com/ Windows* 7 Microsoft* http://windows.microsoft.com Note: For more information on the software listed in this table, contact the manufacturer of the software directly. -

Bringing Two SGET Standards Together

boards & solutions + Combined Print Magazine for the European Embedded Market November 06/15 COVER STORY: Modular embedded NUC systems with Qseven modules Bringing two SGET Standards together SPECIAL FEATURES: SPECIAL ISSUE Boards & Modules Industrial Control Industrial Communications Industrial Internet-of-Things VIEWPOINT Dear Readers, And once again its show time! Beside the exhibition Embedded World in springtime there is another import- ant event for the embedded com- munity in Germany: SPS IPC Drives in fall. This year this international exhibition for industrial automa- tion will be held from 24th to 26th of November in the Exhibition Cen- tre in Nuremberg. More than 1,600 exhibitors including all key players in this industry will present their innovations and trend-setting new products as well as future technolo- gies. Main focus of many exhibitors this year will be Industrie 4.0. To simplify it for visitors getting infor- mation about this important topic the organizer created for the first time the “Industrie 4.0 Area” in Hall 3A. In this area there will be the joint stand and forum “Automation meets IT” which will present data based business models as well as IT based automation solutions for the future digital production. The joint stand “MES goes Automation“ will show how the use of MES optimizes order processing and production processes. The special show space SmartFactory will demonstrate the multi-vendor intelligent factory of the future. Industry associations ZVEI in hall 2 and VDMA in hall 3 will offer competent lectures and panel discussions about actual topics. The joint stands “AMA Centre for Sensors, Test and Measurement” and VDMA´s “Machine Vision” in hall 4A as well as “Wireless in Automation” will inform visitors extensive about the respective topics. -

Intel Next Unit of Computing Kit DC53427HYE UCFF, 1 X Core I5 3427U / 1.8 Ghz, RAM 0 MB, No HDD, HD Graphics 4000, Gigabit LAN, No OS, Vpro, Monitor : None

Siewert & Kau Computertechnik GmbH Walter-Gropius-Str. 12a DE 50126 Bergheim Telephone: 02271 - 763 0 Fax: 02271 - 763 280 E-Mail: [email protected] Internet: http://www.siewert-kau.com Intel Next Unit of Computing Kit DC53427HYE UCFF, 1 x Core i5 3427U / 1.8 GHz, RAM 0 MB, no HDD, HD Graphics 4000, Gigabit LAN, no OS, vPro, Monitor : none. A revolution in ultra-compact device design, Intel NUC packages a fully scalable, computing solution in the smallest possible form factor, complete with the Intel Core i5 processor. This computing device provides a flexible, customizable engine to drive digital signage, kiosks, and intelligent computing for small spaces, or anywhere else you can imagine. General information Intel Category Desktops & Servers Article number 103267 BOXDC53427HYE Technical specifications Product Description Intel Next Unit of Computing Kit DC53427HYE - Core i5 3427U 1.8 GHz - Monitor : none. Type PC barebone Platform Technology Intel vPro Technology Form Factor Ultra compact form factor Processor 1 x Intel Core i5 (3rd Gen) 3427U / 1.8 GHz ( 2.8 GHz ) ( Dual-Core ) Processor Main Features Hyper-Threading Technology, Intel Execute Disable Bit, Enhanced Intel SpeedStep Technology, Intel Virtualization Technology, Intel Turbo Boost Technology 2, Intel 64 Technology Cache Memory 3 MB Cache Per Processor 3 MB RAM 0 MB (installed) / 16 GB (max) - DDR3 SDRAM Hard Drive No HDD Monitor None. Graphics Controller Intel HD Graphics 4000 Audio Output Integrated - 7.1 channel surround Networking Gigabit LAN OS Provided No operating -

Intel Edison Tutorial – Introduction to Linux After Completing This Tutorial

Intel® Edison Tutorial: Introduction, Linux Operating System Shell Access and SFTP Intel® Edison Tutorial: Introduction, Linux Operating System Shell Access and SFTP 1 Table of Contents Introduction ......................................................................... Error! Bookmark not defined. List of Required Equipment and Materials ................................................................... 3 Intel Edison Overview .................................................................................................... 4 Key Features ........................................................................................................................... 4 Assembly ........................................................................................................................ 5 Linux Operating System Shell Access – Serial Terminal Connection ...................... 8 Hardware Setup ...................................................................................................................... 8 Windows Operating System ................................................................................................ 10 Apple Mac OS-X Operating System .................................................................................... 13 Linux Operating System ...................................................................................................... 13 Login and Setup ................................................................................................................... 14 Enabling SSH Access -

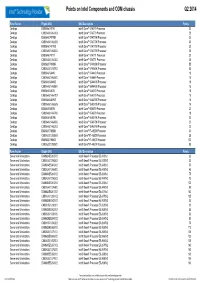

Q2 Matrix Final.Xlsx

Points on Intel Components and ODM chassis Q2 2014 Form Factor Eligble SKU SKU Description Points Desktop BX80646I74770 Intel® Core™ i7-4770 Processor 30 Desktop CM8064601464303 Intel® Core™ i7-4770 Processor 28 Desktop BX80646I74770K Intel® Core™ i7-4770K Processor 32 Desktop CM8064601464206 Intel® Core™ i7-4770K Processor 30 Desktop BX80646I74770S Intel® Core™ i7-4770S Processor 30 Desktop CM8064601465504 Intel® Core™ i7-4770S Processor 28 Desktop BX80646I74771 Intel® Core™ i7-4771 Processor 30 Desktop CM8064601464302 Intel® Core™ i7-4771 Processor 28 Desktop BX80633I74930K Intel® Core™ i7-4930K Processor 55 Desktop CM8063301292702 Intel® Core™ i7-4930K Processor 53 Desktop BX80646I54440 Intel® Core™ i5-4440 Processor 18 Desktop CM8064601464800 Intel® Core™ i5-4440 Processor 16 Desktop BX80646I54440S Intel® Core™ i5-4440S Processor 18 Desktop CM8064601465804 Intel® Core™ i5-4440S Processor 16 Desktop BX80646I54570 Intel® Core™ i5-4570 Processor 18 Desktop CM8064601464707 Intel® Core™ i5-4570 Processor 16 Desktop BX80646I54570S Intel® Core™ i5-4570S Processor 18 Desktop CM8064601465605 Intel® Core™ i5-4570S Processor 16 Desktop BX80646I54670 Intel® Core™ i5-4670 Processor 20 Desktop CM8064601464706 Intel® Core™ i5-4670 Processor 18 Desktop BX80646I54670K Intel® Core™ i5-4670K Processor 22 Desktop CM8064601464506 Intel® Core™ i5-4670K Processor 20 Desktop CM8064601465703 Intel® Core™ i5-4670S Processor 20 Desktop BX80633I74820K Intel® Core™i7-4820K Processor 30 Desktop CM8063301292805 Intel® Core™i7-4820K Processor 28 Desktop BX80633I74960X