Designing with Low-Dropout Voltage Regulators

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Op-Amp Comparators Model of a Schmitt Trigger

1 Electronic Instrumentation Experiment 6 -- Digital Switching Part A: Transistor Switches Part B: Comparators and Schmitt Triggers Part C: Digital Switching Part D: Switching a Relay Part A: Transistors Analog Circuits vs. Digital Circuits Bipolar Junction Transistors Transistor Characteristics Using Transistors as Switches 2 Analog Circuits vs. Digital Circuits An analog signal is an electric signal whose value varies continuously over time. A digital signal can take on only finite values as the input varies over time. 3 • A binary signal, the most common digital signal, is a signal that can take only one of two discrete values and is therefore characterized by transitions between two states. • In binary arithmetic, the two discrete values f1 and f0 are represented by the numbers 1 and 0, respectively. 4 • In binary voltage waveforms, these values are represented by two voltage levels. • In TTL convention, these values are nominally 5V and 0V, respectively. • Note that in a binary waveform, knowledge of the transition between one state and another is equivalent to knowledge of the state. Thus, digital logic circuits can operate by detecting transitions between voltage levels. The transitions are called edges and can be positive (f0 to f1) or negative (f1 to f0). 1 positive negative positive edge 0 edges edge 5 Bipolar Junction Transistors The bipolar junction transistor (BJT) is the salient invention that led to the electronic age, integrated circuits, and ultimately the entire digital world. The transistor is the principal active device in electrical circuits. When inputs are kept relatively small, the transistor serves as an amplifier. When the transistor is overdriven, it acts as a switch, a mode most useful in digital electronics. -

Basics of Linear Regulators ,Application Note

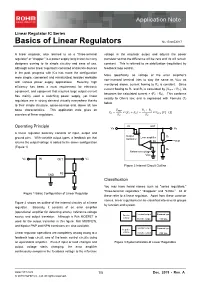

Linear Regulator IC Series Basics of Linear Regulators No.15020EAY17 A linear regulator, also referred to as a "three-terminal voltage in the regulator output and adjusts the power regulator" or "dropper," is a power supply long known to many transistor so that the difference will be zero and Vo will remain designers owning to its simple circuitry and ease of use. constant. This is referred to as stabilization (regulation) by Although some linear regulators consisted of discrete devices feedback loop control. in the past, progress with ICs has made the configuration More specifically, as voltage of the error amplifier's more simple, convenient and miniaturized, besides workable non-inversed terminal tries to stay the same as VREF as with various power supply applications. Recently, high mentioned above, current flowing to R2 is constant. Since efficiency has been a must requirement for electronic current flowing to R1 and R2 is calculated by (VREF / R2), Vo equipment, and equipment that requires large output current becomes the calculated current × (R1+R2). This conforms has mainly used a switching power supply, yet linear exactly to Ohm’s law, and is expressed with Formula (1) regulators are in strong demand virtually everywhere thanks below. to their simple structure, space-savings and, above all, low noise characteristics. This application note gives an 1 overview of linear regulators. Operating Principle IN OUT VIN VO A linear regulator basically consists of input, output and Output Error amplifier R1 ground pins. With variable output types, a feedback pin that transistor FB =VREF returns the output voltage is added to the above configuration + (Figure 1). -

A Low Dropout, CMOS Regulator with High PSR Over Wideband Frequencies Vishal Gupta, Student Member, IEEE, and Gabriel A

A Low Dropout, CMOS Regulator with High PSR over Wideband Frequencies Vishal Gupta, Student Member, IEEE, and Gabriel A. Rincón-Mora, Member, IEEE Abstract- Modern System-on-Chip (SoC) environments are advance towards integration, these state-of-the-art regulators swamped in high frequency noise that is generated by RF and are increasingly integrated “on-chip” and deployed at the digital circuits and propagated onto supply rails through point-of-load, with output currents in the range of 10 – 50 mA capacitive coupling. In these systems, linear regulators are used [9]–[15]. This strategy allows the regulators to be optimized to to shield noise-sensitive analog blocks from high frequency fluctuations in the power supply. This work presents a low cater to the specific demands of the sub-systems that load dropout regulator that achieves Power Supply Rejection (PSR) them [4]. Also, on-chip capacitors (10-200 pF) can often be better than -40dB over the entire frequency spectrum. The used for frequency compensation [9]-[15], thereby conserving system has an output voltage of 1.0V and a maximum current board-space and leading to increasing levels of integration. capability of 10mA. It consists of operational amplifiers (op Since the regulators do not use an external capacitor to amps), a bandgap reference, a clock generator, and a charge establish the dominant low-frequency pole, they are termed pump and has been designed and simulated using BSIM3 models “internally compensated regulators”. of a 0.5µm CMOS process obtained from MOSIS. In this work, the basic linear regulator and current schemes I. -

A Two-Module Linear Regulator with 3.9–10 V Input, 2.5 V Output, and 500 Ma Load

electronics Article A Two-Module Linear Regulator with 3.9–10 V Input, 2.5 V Output, and 500 mA Load Quanzhen Duan 1, Weidong Li 1, Shengming Huang 1,*, Yuemin Ding 2,*, Zhen Meng 3 and Kai Shi 2 1 School of Electrical and Electronic Engineering and Tianjin Key Laboratory of Film Electronic and Communication Devices, Tianjin University of Technology, Tianjin 300384, China; [email protected] (Q.D.); [email protected] (W.L.) 2 School of Computer and Science Engineering, Tianjin University of Technology, Tianjin 300384, China; [email protected] 3 Institute of Microelectronics of the Chinese Academy of Sciences, Beijing 100029, China; [email protected] * Correspondence: [email protected] (S.H.); [email protected] (Y.D.) Received: 7 September 2019; Accepted: 4 October 2019; Published: 10 October 2019 Abstract: A linear regulator with an input range of 3.9–10 V, 2.5 V output, and a maximal 500 mA load for use with battery systems was developed and presented here. The linear regulator featured two modules of a preregulator and a linear regulator core circuit, offering minimized power dissipation and high-level stability. The preregulator delivered an internal power voltage of 3 V and supplied internal circuits including the second module (the linear regulator core). The preregulator fitted with an active, low-pass filter provided a low-noise reference voltage to the linear regulator core circuit. To ensure operational stability for the linear regulator, error amplifiers incorporating the Miller compensation technique and featuring a large slewing rate were employed in the two modules. -

Design of CMOS Schmitt Trigger Munish Kumar, Parminder Kaur, Sheenu Thapar

ISSN: 2277-3754 ISO 9001:2008 Certified International Journal of Engineering and Innovative Technology (IJEIT) Volume 2, Issue 1, July 2012 Design of CMOS Schmitt Trigger Munish Kumar, Parminder Kaur, Sheenu Thapar voltage is applied at the input, both M1 andM2 are in OFF Abstract— This paper presents comparison among various condition while M4 and M5 are in ON condition and output Schmitt triggers on the basis of their hysteresis width and is at high logic level. When the input reaches to threshold average power consumed. Hysteresis width is improved by using voltage of M1 transistor then M1 will be on , while M2 two feedback loops as compared to conventional CMOS Schmitt trigger whose hysteresis width is fixed. All Schmitt trigger remains OFF and at this time output will be high M3 will be circuits have been realized using .25um and .18µm CMOS on , so M1 Try to pull down the node between M1 and M2 technology and simulation results are presented. while M3 try to pulls up this node to voltage VDD-VT , so transistor M2 stays the output to HIGH logic level , now Index Terms— Hysteresis Width, Static Power Dissipation, Dynamic Power Dissipation. when the input rises up to the threshold voltage of M2 then output switches to low logic level, so effectively our I. INTRODUCTION switching point shifted to higher voltage referred as VIH. Similar in case when input is falling from higher logic level Schmitt triggers are bistable networks that are widely used then PMOS‘s comes into picture and switching point at to enhance the immunity of a circuit to noise and output is shifted to some lower voltage referred as VIH. -

Voltage Regulator Solutions for Xilinx Virtex Edual Voltage Fpgas

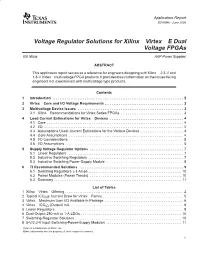

Application Report SLVA086 - June 2000 Voltage Regulator Solutions for Xilinx Virtex E Dual Voltage FPGAs Bill Milus AAP Power Supplies ABSTRACT This application report serves as a reference for engineers designing with Xilinx 2.5-V and 1.8-V Virtex multivoltage FPGA products. It provides basic information on the issues facing engineers not experienced with multivoltage type products. Contents 1 Introduction . 2 2 Virtex Core and I/O Voltage Requirements. 2 3 Multivoltage Device Issues. 3 3.1 Xilinx Recommendations for Virtex Series FPGAs. 3 4 Load Current Estimations for Virtex Devices. 4 4.1 Core . 4 4.2 I/O . 4 4.3 Assumptions Used: Current Estimations for the Various Devices. 4 4.4 Core Assumptions . 4 4.5 I/O Considerations . 5 4.6 I/O Assumptions . 5 5 Supply Voltage Regulator Options. 7 5.1 Linear Regulators . 7 5.2 Inductive Switching Regulators. 7 5.3 Inductive Switching Power-Supply Module. 8 6 TI Recommended Solutions. 9 6.1 Switching Regulators ≥ 3 Amps. 10 6.2 Power Modules (Power Trends). 10 6.3 Summary . 11 List of Tables 1 Xilinx Virtex Offering . 2 2 Typical ICCINT Current Draw for Virtex Family. 5 3 Virtex Maximum User I/O Available in Package. 6 4 Virtex ICCIO (Output) mA. 6 5 Linear Regulators . 9 6 Dual-Output 250-mA to 1-A LDOs. 10 7 Switching-Regulator Solutions. 10 8 5-V/3.3-V Input Switching-Power-Supply Modules. 11 Virtex is a trademark of Xilinx, Inc. Other trademarks are the property of their respective owners. 1 SLVA086 1 Introduction Many devices, such as digital signal processors (DSP), microprocessors, and field- programmable gate arrays (FPGA), are designed to consume minimum power while providing high performance at low cost. -

Low Power Schmitt Trigger

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by International Institute for Science, Technology and Education (IISTE): E-Journals Innovative Systems Design and Engineering www.iiste.org ISSN 2222-1727 (Paper) ISSN 2222-2871 (Online) Vol 3, No 2, 2012 Low Power Schmitt Trigger Swati Kundra *, Priyanka Soni Mody Institute of Technology & Science, Lakshmangarh-332311, India * E-mail of the corresponding author: [email protected] Abstract The Schmitt Trigger is a comparator circuit that incorporates positive feedback. Noise is being ignored by CMOS Schmitt Trigger as the hysteresis in a Schmitt Trigger circuit offers a better noise margin and noise stable operation. And the simulation has been done on Tanner EDA tool at TSMC 130nm technology with 1 V supply voltage. TSPICE simulation results of the circuit confirm the effectiveness of the approach. Proposed Schmitt Trigger is designed by using less transistor count and a capacitor which results in less average power consumption with decrease in area. Delay is also decreased by using only one PMOS as because delay is more concentrated to PMOS due to less mobility of PMOS compare to NMOS. Keywords: CMOS Schmitt Trigger, Delay, Low power consumption 1. Introduction Sometimes an input signal to a digital circuit doesn’t directly fit the description of a digital signal. For various reasons it may have slow rise and/or fall times, or may have acquired some noise that could be sensed by further circuitry. It may even be an analog signal whose frequency we want to measure. All of these conditions, and many others, require a specialized circuit that will “clean up” a signal and force it to true digital shape. -

ADP1762 (Rev. D)

2 A, Low VIN, Low Noise, CMOS Linear Regulator Data Sheet ADP1762 FEATURES TYPICAL APPLICATION CIRCUITS 2 A maximum output current ADP1762 VIN = 1.7V VOUT = 1.5V Low input voltage supply range VIN VOUT CIN COUT 10µF 10µF VIN = 1.10 V to 1.98 V, no external bias supply required SENSE Fixed output voltage range: VOUT_FIXED = 0.9 V to 1.5 V RPULL-UP ON 100kΩ EN Adjustable output voltage range: VOUT_ADJ = 0.5 V to 1.5 V PG PG OFF Ultralow noise: 2 μV rms, 100 Hz to 100 kHz SS VADJ Noise spectral density CSS VREG REFCAP 10nF C 4 nV/√Hz at 10 kHz CREG GND REF 1µF 1µF 3 nV/√Hz at 100 kHz 12922-001 Low dropout voltage: 62 mV typical at 2 A load Figure 1. Fixed Output Operation Operating supply current: 4.5 mA typical at no load ADP1762 VIN = 1.7V VOUT = 1.5V ±1.5% fixed output voltage accuracy over line, load, and VIN VOUT CIN COUT temperature 10µF 10µF SENSE Excellent power supply rejection ratio (PSRR) performance RPULL-UP ON 100kΩ EN 62 dB typical at 10 kHz at 2 A load PG PG OFF 46 dB typical at 100 kHz at 2 A load SS VADJ Excellent load/line transient response CSS VREG REFCAP RADJ 10nF C 10kΩ Soft start to reduce inrush current CREG GND REF 1µF 1µF Optimized for small 10 μF ceramic capacitors 12922-002 Current-limit and thermal overload protection Figure 2. Adjustable Output Operation Power-good indicator Table 1. Related Devices Precision enable Input Maximum Fixed/ 16-lead, 3 mm × 3 mm LFCSP package Device Voltage Current Adjustable Package AEC-Q100 qualified for automotive applications ADP1761 1.10 V to 1 A Fixed/adjustable 16-lead 1.98 -

Low-Voltage Cutoff Circuits

jfsimon – June 2018 Low-voltage cutoff circuits Using a TL431 or similar: Battery Guardian (Silicon Chip, 2002) http://www.qsl.net/9w2lw/guardian.htm LM336, comparator, N-channel MOSFET on high side driven by isolated SMPS Forum post, LV alarm, MikeML (15 March 2010) https://www.electro-tech-online.com/threads/12v-battery-low-voltage-monitor.104886/#post-856427 TL431, LED driven by NPN BJT Forum post, LV disconnect 1, MikeML (4 February 2011) https://www.electro-tech-online.com/threads/12v-battery-low-voltage-monitor.104886/page-2#post-950306 TL431, P-channel MOSFET, hysteresis resistor Same circuit from RONV (13 February 2016) https://forum.allaboutcircuits.com/threads/voltage-cut-off-tl431.120827/#post-965055 Same circuit from Hero999 (20 February 2017) https://www.eevblog.com/forum/projects/power-the-load-only-when-car-supply-voltage-is-above-14- volts/msg1140485/#msg1140485 Variant of the same circuit with ATL431 (20 February 2017) https://www.eevblog.com/forum/projects/power-the-load-only-when-car-supply-voltage-is-above-14- volts/msg1140526/#msg1140526 Forum post, LV disconnect 2, MikeML (11 February 2014) https://forum.allaboutcircuits.com/threads/tl431-battery-cut-off.94148/#post-696553 TL431, P-channel MOSFET, push-button, battery voltage is measured at MOSFET drain Forum post, Ian.M (9 August 2016) https://www.eevblog.com/forum/renewable-energy/efficient-way-to-disconnect-battery-when-voltage- drops/msg1000473/#msg1000473 TL431, NPN emitter follower, Schottky diode, P-channel MOSFET jfsimon – June 2018 Driving a relay directly with a TL431, push button to start Note: I tested this one but I haven’t been able to get reliable triggering of the relay. -

Section 1 Point-Of-Load Power

Point-of-Load Power Practical Power Solutions 1. Point-of-Load Power 2. System Power Management and Portable Power 3. Power for Mixed Analog/Digital Systems 4. Hardware Design Techniques Copyright © 2009 By Analog Devices, Inc. All rights reserved. This book, or parts thereof, must not be reproduced in any form without permission of the copyright owner. SECTION 1 POINT-OF-LOAD POWER Fixed Power Point-of-Load Applications....................................................................1.1 Linear Regulators..........................................................................................................1.9 Switching Regulators and Controllers.....................................................................1.26 Powering FPGAs.........................................................................................................1.41 Powering DSPs.............................................................................................................1.51 ADIsimPower Design Tool...........................................................................................1.57 Technical References..............................................................................................1.68 1.0 Point-of-Load Power Fixed Power Point-of-Load Applications Today's system power requirements have become quite challenging, and design engineers must deal with multiple supply voltages, sequencing issues, high transient load currents, thermal considerations, and many others. In most cases, these problems must be addressed at the PC -

Full On-Chip CMOS Low-Dropout Voltage Regulator Robert J

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, VOL. 54, NO. 9, SEPTEMBER 2007 1879 Full On-Chip CMOS Low-Dropout Voltage Regulator Robert J. Milliken, Jose Silva-Martínez, Senior Member, IEEE, and Edgar Sánchez-Sinencio, Fellow, IEEE Abstract—This paper proposes a solution to the present bulky external capacitor low-dropout (LDO) voltage regulators with an external capacitorless LDO architecture. The large external capac- itor used in typical LDOs is removed allowing for greater power system integration for system-on-chip (SoC) applications. A com- pensation scheme is presented that provides both a fast transient response and full range alternating current (ac) stability from 0- to 50-mA load current even if the output load is as high as 100 pF. The 2.8-V capacitorless LDO voltage regulator with a power supply of 3 V was fabricated in a commercial 0.35- m CMOS technology, consuming only 65 A of ground current with a dropout voltage of 200 mV. Experimental results demonstrate that the proposed ca- Fig. 1. External capacitorless LDO voltage regulator. pacitorless LDO architecture overcomes the typical load transient and ac stability issues encountered in previous architectures. Index Terms—Analog circuits, capacitorless low dropout (LDO), The conventional LDO voltage regulator, for stability require- dc–dc regulator, fast path, LDO voltage regulators, transient com- ments, requires a relatively large output capacitor in the single pensation. microfarad range. Large microfarad capacitors cannot be real- ized in current design technologies, thus each LDO regulator I. INTRODUCTION needs an external pin for a board mounted output capacitor. To overcome this issue, a capacitorless LDO has been proposed in NDUSTRY is pushing towards complete system-on-chip [2]; that topology is, however, unstable at low currents making (SoC) design solutions that include power management. -

MM74C14 Hex Schmitt Trigger

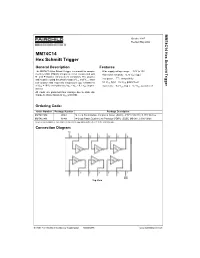

MM74C14 Hex Schmitt Trigger Hex Schmitt MM74C14 October 1987 Revised May 2002 MM74C14 Hex Schmitt Trigger General Description Features The MM74C14 Hex Schmitt Trigger is a monolithic comple- ■ Wide supply voltage range: 3.0V to 15V mentary MOS (CMOS) integrated circuit constructed with ■ High noise immunity: 0.70 VCC (typ.) N- and P-channel enhancement transistors. The positive ■ Low power: TTL compatibility: and negative going threshold voltages VT+ and VT−, show low variation with respect to temperature (typ. 0.0005V/°C 0.4 VCC (typ.) 0.2 VCC guaranteed = − ≥ ■ at VCC 10V), and hysteresis, VT+ VT− 0.2 VCC is guar- Hysteresis: 0.4 VCC (typ.): 0.2 VCC guaranteed anteed. All inputs are protected from damage due to static dis- charge by diode clamps to VCC and GND. Ordering Code: Order Number Package Number Package Description MM74C14M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow MM74C14N N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Devices also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code. Connection Diagram Top View © 2002 Fairchild Semiconductor Corporation DS005879 www.fairchildsemi.com Absolute Maximum Ratings(Note 1) − + Voltage at Any Pin 0.3Vto VCC 0.3V Operating Temperature Range −55°C to +125°C MM74C14 Storage Temperature Range −65°C to +150°C Power Dissipation Dual-In-Line 700 mW Note 1: “Absolute Maximum Ratings” are those values beyond which the Small Outline 500mW safety of the device cannot be guaranteed. Except for “Operating Tempera- Operating V Range 3.0V to 15V ture Range” they are not meant to imply that the devices should be oper- CC ated at these limits.