F09 Quake II

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

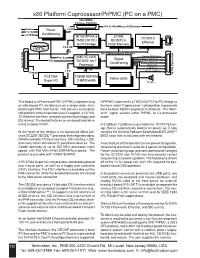

X86 Platform Coprocessor/Prpmc (PC on a PMC)

x86 Platform Coprocessor/PrPMC (PC on a PMC) 32b/33MHz PCI bus PN1/PN2 +5V to Kbd/Mouse/USB power Vcore Power +3.3V +2.5v Conditioning +3.3VIO 1K100 FPGA & 512KB 10/100TX TMS2250 PCI BIOS/PLA Ethernet RJ45 Compact to PCI bridge Flash Memory PLA I/O Flash site 8 32b/33MHz Internal PCI bus Analog SVGA Video Pwr Seq AMD SC2200 Signal COM 1 (RXD/TXD only) IDE "GEODE (tm)" Conditioning COM 2 (RXD/TXD only) Processor USB Port 1 Rear I/O PN4 I/O Rear 64 USB Port 2 LPC Keyboard/Mouse Floppy 36 Pin 36 Pin Connector PC87364 128MB SDRAM Status LEDs Super I/O (16MWx64b) PC Spkr This board is a Processor PMC (PrPMC) implementing A PrPMC implements a TMS2250 PCI-to-PCI bridge to an x86-based PC architecture on a single-wide, stan- the host, and a “Coprocessor” cofniguration implements dard height PMC form factor. This delivers a complete back-to-back 16550 compatible COM ports. The “Mon- x86 platform with comprehensive I/O support, a 10/100- arch” signal selects either PrPMC or Co-processor TX Ethernet interface, and disk access (both floppy and mode. IDE drives). The board features an on-board hard drive using Compact Flash. A 512Kbyte FLASH memory holds the 1K100 PLA im- age that is automatically loaded on power up. It also At the heart of the design is an Advanced Micro De- contains the General Software Embedded BIOS 2000™ vices SC2200 GEODE™ processor that integrates video, BIOS code that is included with each board. -

Convey Overview

THE WORLD’S FIRST HYBRID-CORE COMPUTER. CONVEY HYBRID-CORE COMPUTING Hybrid-core Computing Convey HC-1 High Performance of application- specific hardware Heterogenous solutions • can be much more efficient Performance/ • still hard to program Programmability and Power efficiency deployment ease of an x86 server Application Multicore solutions • don’t always scale well • parallel programming is hard Low Difficult Ease of Deployment Easy 1/22/2010 3 Hybrid-Core Computing Application-Specific Personalities Applications • Extend the x86 instruction set • Implement key operations in Convey Compilers hardware Life Sciences x86-64 ISA Custom ISA CAE Custom Financial Oil & Gas Shared Virtual Memory Cache-coherent, shared memory • Both ISAs address common memory *ISA: Instruction Set Architecture 7/12/2010 4 HC-1 Hardware PCI I/O FPGA FPGA Intel Personalities Chipset FPGA FPGA 8 GB/s 80 GB/s Memory Memory Cache Coherent, Shared Virtual Memory 1/22/2010 5 Using Personalities C/C++ Fortran • Personalities are user specifies reloadable personality at instruction sets Convey Software compile time Development Suite • Compiler instruction generates x86 descriptions and coprocessor instructions from Hybrid-Core Executable P ANSI standard x86-64 and Coprocessor Personalities C/C++ & Fortran Instructions • Executable can run on x86 nodes FPGA Convey HC-1 or Convey Hybrid- bitfiles Core nodes Intel x86 Coprocessor personality loaded at runtime by OS 1/22/2010 6 SYSTEM ARCHITECTURE HC-1 Architecture “Commodity” Intel Server Convey FPGA-based coprocessor Direct -

Haxe Game Development Essentials

F re e S a m p le Community Experience Distilled Haxe Game Development Essentials Create games on multiple platforms from a single codebase using Haxe and the HaxeFlixel engine Jeremy McCurdy In this package, you will find: The author biography A preview chapter from the book, Chapter 1 'Getting Started' A synopsis of the book’s content More information on Haxe Game Development Essentials About the Author Jeremy McCurdy is a game developer who has been making games using ActionScript, C#, and Haxe for over four years. He has developed games targeted at iOS, Android, Windows, OS X, Flash, and HTML5. He has worked on games that have had millions of gameplay sessions, and has built games for many major North American television networks. He is the games technical lead at REDspace, an award-winning interactive studio that has worked for some of the world's largest brands. They are located in Nova Scotia, Canada, and have been building awesome experiences for 15 years. Preface Developing games that can reach a wide audience can often be a serious challenge. A big part of the problem is fi guring out how to make a game that will work on a wide range of hardware and operating systems. This is where Haxe comes in. Over the course of this book, we'll look at getting started with Haxe and the HaxeFlixel game engine, build a side-scrolling shooter game that covers the core features you need to know, and prepare the game for deployment to multiple platforms. After completing this book, you will have the skills you need to start producing your own cross-platform Haxe-driven games! What this book covers Chapter 1, Getting Started, explains setting up the Haxe and HaxeFlixel development environment and doing a quick Hello World example to ensure that everything is working. -

Master Thesis

Faculty of Computer Science and Management Field of study: COMPUTER SCIENCE Specialty: Information Systems Design Master Thesis Multithreaded game engine architecture Adrian Szczerbiński keywords: game engine multithreading DirectX 12 short summary: Project, implementation and research of a multithreaded 3D game engine architecture using DirectX 12. The goal is to create a layered architecture, parallelize it and compare the results in order to state the usefulness of multithreading in game engines. Supervisor ...................................................... ............................ ……………………. Title/ degree/ name and surname grade signature The final evaluation of the thesis Przewodniczący Komisji egzaminu ...................................................... ............................ ……………………. dyplomowego Title/ degree/ name and surname grade signature For the purposes of archival thesis qualified to: * a) Category A (perpetual files) b) Category BE 50 (subject to expertise after 50 years) * Delete as appropriate stamp of the faculty Wrocław 2019 1 Streszczenie W dzisiejszych czasach, gdy społeczność graczy staje się coraz większa i stawia coraz większe wymagania, jak lepsza grafika, czy ogólnie wydajność gry, pojawia się potrzeba szybszych i lepszych silników gier, ponieważ większość z obecnych jest albo stara, albo korzysta ze starych rozwiązań. Wielowątkowość jest postrzegana jako trudne zadanie do wdrożenia i nie jest w pełni rozwinięta. Programiści często unikają jej, ponieważ do prawidłowego wdrożenia wymaga wiele pracy. Według mnie wynikający z tego wzrost wydajności jest warty tych kosztów. Ponieważ nie ma wielu silników gier, które w pełni wykorzystują wielowątkowość, celem tej pracy jest zaprojektowanie i zaproponowanie wielowątkowej architektury silnika gry 3D, a także przedstawienie głównych systemów używanych do stworzenia takiego silnika gry 3D. Praca skupia się na technologii i architekturze silnika gry i jego podsystemach wraz ze strukturami danych i algorytmami wykorzystywanymi do ich stworzenia. -

Building a Java First-Person Shooter

3D Java Game Programming – Episode 0 Building a Java First-Person Shooter Episode 0 [Last update: 5/03/2017] These notes are intended to accompany the video sessions being presented on the youtube channel “3D Java Game Programming” by youtube member “The Cherno” at https://www.youtube.com/playlist?list=PL656DADE0DA25ADBB. I created them as a way to review the material and explore in more depth the topics presented. I am sharing with the world since the original work is based on material freely and openly available. Note: These notes DO NOT stand on their own, that is, I rely on the fact that you viewed and followed along the video and may want more information, clarification and or the material reviewed from a different perspective. The purpose of the videos is to create a first-person shooter (FPS) without using any Java frameworks such as Lightweight Java Game Library (LWJGL), LibGDX, or jMonkey Game Engine. The advantages to creating a 3D FPS game without the support of specialized game libraries that is to limit yourself to the commonly available Java classes (not even use the Java 2D or 3D APIs) is that you get to learn 3D fundamentals. For a different presentation style that is not geared to following video episodes checkout my notes/book on “Creating Games with Java.” Those notes are more in a book format and covers creating 2D and 3D games using Java in detail. In fact, I borrow or steal from these video episode notes quite liberally and incorporate into my own notes. Prerequisites You should be comfortable with basic Java programming knowledge that would be covered in the one- semester college course. -

GWT + HTML5 Can Do What? (Google I/O 2010)

GWT + HTML5 Can Do What!? Ray Cromwell, Stefan Haustein, Joel Webber May 2010 View live notes and ask questions about this session on Google Wave http://bit.ly/io2010-gwt6 Overview • HTML5 and GWT • Demos 1. Eyes 2. Ears 3. Guns What is HTML5 • Formal definition o Best practices for HTML interpretation o Audio and Video elements o Other additional elements • Colloquial meaning o Canvas o WebGL o WebSockets o CSS 3 o LocalStorage o et al GWT support for HTML5 • Very easy to build Java wrappers • Many already exist in open-source projects • Will be moving many of these into GWT proper (~2.2) • Not part of GWT core yet • GWT has always strived to be cross-browser • Most new features are not available on all browsers WebGL • OpenGL ES 2.0, made Javascript-friendly • Started by Canvas3D work at Mozilla • Spread to Safari and Chrome via WebKit • Canvas.getContext("webgl"); WebGL Differences to OpenGL 1.x • No fixed function pipeline (no matrix operations, no predefined surface models) • Supports the GL Shader Language (GLSL) o Extremely flexible o Can be used for fast general computation, too • Distinct concepts of native arrays and buffers o Buffers may be stored in graphics card memory o Arrays provide element-wise access from JS o Data from WebGL Arrays needs to be copied to WebGL buffers before it can be be used in graphics operations Eyes: Image Processing Image Processing Photoshop Filters in the Browser • Work on megapixel images • At interactive frame rates • Provide general purpose operations o scale, convolve, transform, colorspace -

Introducing 2D Game Engine Development with Javascript

CHAPTER 1 Introducing 2D Game Engine Development with JavaScript Video games are complex, interactive, multimedia software systems. These systems must, in real time, process player input, simulate the interactions of semi-autonomous objects, and generate high-fidelity graphics and audio outputs, all while trying to engage the players. Attempts at building video games can quickly be overwhelmed by the need to be well versed in software development as well as in how to create appealing player experiences. The first challenge can be alleviated with a software library, or game engine, that contains a coherent collection of utilities and objects designed specifically for developing video games. The player engagement goal is typically achieved through careful gameplay design and fine-tuning throughout the video game development process. This book is about the design and development of a game engine; it will focus on implementing and hiding the mundane operations and supporting complex simulations. Through the projects in this book, you will build a practical game engine for developing video games that are accessible across the Internet. A game engine relieves the game developers from simple routine tasks such as decoding specific key presses on the keyboard, designing complex algorithms for common operations such as mimicking shadows in a 2D world, and understanding nuances in implementations such as enforcing accuracy tolerance of a physics simulation. Commercial and well-established game engines such as Unity, Unreal Engine, and Panda3D present their systems through a graphical user interface (GUI). Not only does the friendly GUI simplify some of the tedious processes of game design such as creating and placing objects in a level, but more importantly, it ensures that these game engines are accessible to creative designers with diverse backgrounds who may find software development specifics distracting. -

Exploiting Free Silicon for Energy-Efficient Computing Directly

Exploiting Free Silicon for Energy-Efficient Computing Directly in NAND Flash-based Solid-State Storage Systems Peng Li Kevin Gomez David J. Lilja Seagate Technology Seagate Technology University of Minnesota, Twin Cities Shakopee, MN, 55379 Shakopee, MN, 55379 Minneapolis, MN, 55455 [email protected] [email protected] [email protected] Abstract—Energy consumption is a fundamental issue in today’s data A well-known solution to the memory wall issue is moving centers as data continue growing dramatically. How to process these computing closer to the data. For example, Gokhale et al [2] data in an energy-efficient way becomes more and more important. proposed a processor-in-memory (PIM) chip by adding a processor Prior work had proposed several methods to build an energy-efficient system. The basic idea is to attack the memory wall issue (i.e., the into the main memory for computing. Riedel et al [9] proposed performance gap between CPUs and main memory) by moving com- an active disk by using the processor inside the hard disk drive puting closer to the data. However, these methods have not been widely (HDD) for computing. With the evolution of other non-volatile adopted due to high cost and limited performance improvements. In memories (NVMs), such as phase-change memory (PCM) and spin- this paper, we propose the storage processing unit (SPU) which adds computing power into NAND flash memories at standard solid-state transfer torque (STT)-RAM, researchers also proposed to use these drive (SSD) cost. By pre-processing the data using the SPU, the data NVMs as the main memory for data-intensive applications [10] to that needs to be transferred to host CPUs for further processing improve the system energy-efficiency. -

Collaborative Design: Integrating Game Engine to Online Interactive Presentation Tool

COLLABORATIVE DESIGN: INTEGRATING GAME ENGINE TO ONLINE INTERACTIVE PRESENTATION TOOL RAKTUM SALLKACHAT, ARAYA CHOUTGRAJANK Master of Science Program in Computer-Aided Architectural Design Rangsit University, Thailand. [email protected]; [email protected] Abstract. In this research, we aim at the development of a computer- aided collaborative design tool, which supports the online architectural presentation independently from computer platforms and locations. Users are enabled to access the system and collaborate among working team via the Internet. Various online 3D Game engines are explored and evaluated. One 3D Game engine is selected and used as a base engine for the collaborative tool development. The application development will specifically concentrate on real-time presentation, shared representation and understanding among design teams and project owner. Traditional architectural design presentation in collaboration process will be imitated and transformed into digital age online presentation. 1. Introduction Traditionally, design collaboration between designers and clients used to be simply managed by using sketch, two-dimensional drawing, architectural model, and perspective drawing. These traditional tools are essential in architectural design process since they represents some forms of prototypes, which help architects in understanding clients’ needs as well as designing and developing projects that match clients’ expectation. In this information age, computer technology has been playing an important role and gradually replacing the traditional tools. Outcomes from this new digital tool are so real that customers could convincingly experience the design prior to actual construction. The development of architectural-specific application, especially 3-D presentation application, are complex and would need high-end system in both development and implementation phases. -

CUDA What Is GPGPU

What is GPGPU ? • General Purpose computation using GPU in applications other than 3D graphics CUDA – GPU accelerates critical path of application • Data parallel algorithms leverage GPU attributes – Large data arrays, streaming throughput Slides by David Kirk – Fine-grain SIMD parallelism – Low-latency floating point (FP) computation • Applications – see //GPGPU.org – Game effects (FX) physics, image processing – Physical modeling, computational engineering, matrix algebra, convolution, correlation, sorting Previous GPGPU Constraints CUDA • Dealing with graphics API per thread per Shader Input Registers • “Compute Unified Device Architecture” – Working with the corner cases per Context • General purpose programming model of the graphics API Fragment Program Texture – User kicks off batches of threads on the GPU • Addressing modes Constants – GPU = dedicated super-threaded, massively data parallel co-processor – Limited texture size/dimension Temp Registers • Targeted software stack – Compute oriented drivers, language, and tools Output Registers • Shader capabilities • Driver for loading computation programs into GPU FB Memory – Limited outputs – Standalone Driver - Optimized for computation • Instruction sets – Interface designed for compute - graphics free API – Data sharing with OpenGL buffer objects – Lack of Integer & bit ops – Guaranteed maximum download & readback speeds • Communication limited – Explicit GPU memory management – Between pixels – Scatter a[i] = p 1 Parallel Computing on a GPU Extended C • Declspecs • NVIDIA GPU Computing Architecture – global, device, shared, __device__ float filter[N]; – Via a separate HW interface local, constant __global__ void convolve (float *image) { – In laptops, desktops, workstations, servers GeForce 8800 __shared__ float region[M]; ... • Keywords • 8-series GPUs deliver 50 to 200 GFLOPS region[threadIdx] = image[i]; on compiled parallel C applications – threadIdx, blockIdx • Intrinsics __syncthreads() – __syncthreads .. -

Comparing the Power and Performance of Intel's SCC to State

Comparing the Power and Performance of Intel’s SCC to State-of-the-Art CPUs and GPUs Ehsan Totoni, Babak Behzad, Swapnil Ghike, Josep Torrellas Department of Computer Science, University of Illinois at Urbana-Champaign, Urbana, IL 61801, USA E-mail: ftotoni2, bbehza2, ghike2, [email protected] Abstract—Power dissipation and energy consumption are be- A key architectural challenge now is how to support in- coming increasingly important architectural design constraints in creasing parallelism and scale performance, while being power different types of computers, from embedded systems to large- and energy efficient. There are multiple options on the table, scale supercomputers. To continue the scaling of performance, it is essential that we build parallel processor chips that make the namely “heavy-weight” multi-cores (such as general purpose best use of exponentially increasing numbers of transistors within processors), “light-weight” many-cores (such as Intel’s Single- the power and energy budgets. Intel SCC is an appealing option Chip Cloud Computer (SCC) [1]), low-power processors (such for future many-core architectures. In this paper, we use various as embedded processors), and SIMD-like highly-parallel archi- scalable applications to quantitatively compare and analyze tectures (such as General-Purpose Graphics Processing Units the performance, power consumption and energy efficiency of different cutting-edge platforms that differ in architectural build. (GPGPUs)). These platforms include the Intel Single-Chip Cloud Computer The Intel SCC [1] is a research chip made by Intel Labs (SCC) many-core, the Intel Core i7 general-purpose multi-core, to explore future many-core architectures. It has 48 Pentium the Intel Atom low-power processor, and the Nvidia ION2 (P54C) cores in 24 tiles of two cores each. -

Re-Purposing Commercial Entertainment Software for Military Use

Calhoun: The NPS Institutional Archive Theses and Dissertations Thesis Collection 2000-09 Re-purposing commercial entertainment software for military use DeBrine, Jeffrey D. Monterey, California. Naval Postgraduate School http://hdl.handle.net/10945/26726 HOOL NAV CA 9394o- .01 NAVAL POSTGRADUATE SCHOOL Monterey, California THESIS RE-PURPOSING COMMERCIAL ENTERTAINMENT SOFTWARE FOR MILITARY USE By Jeffrey D. DeBrine Donald E. Morrow September 2000 Thesis Advisor: Michael Capps Co-Advisor: Michael Zyda Approved for public release; distribution is unlimited REPORT DOCUMENTATION PAGE Form Approved OMB No. 0704-0188 Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington DC 20503. 1 . AGENCY USE ONLY (Leave blank) 2. REPORT DATE REPORT TYPE AND DATES COVERED September 2000 Master's Thesis 4. TITLE AND SUBTITLE 5. FUNDING NUMBERS Re-Purposing Commercial Entertainment Software for Military Use 6. AUTHOR(S) MIPROEMANPGS00 DeBrine, Jeffrey D. and Morrow, Donald E. 8. PERFORMING 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) ORGANIZATION REPORT Naval Postgraduate School NUMBER Monterey, CA 93943-5000 9. SPONSORING / MONITORING AGENCY NAME(S) AND ADDRESS(ES) 10. SPONSORING/ Office of Economic & Manpower Analysis MONITORING AGENCY REPORT 607 Cullum Rd, Floor IB, Rm B109, West Point, NY 10996-1798 NUMBER 11.