14:332:331 Midterm Exam II

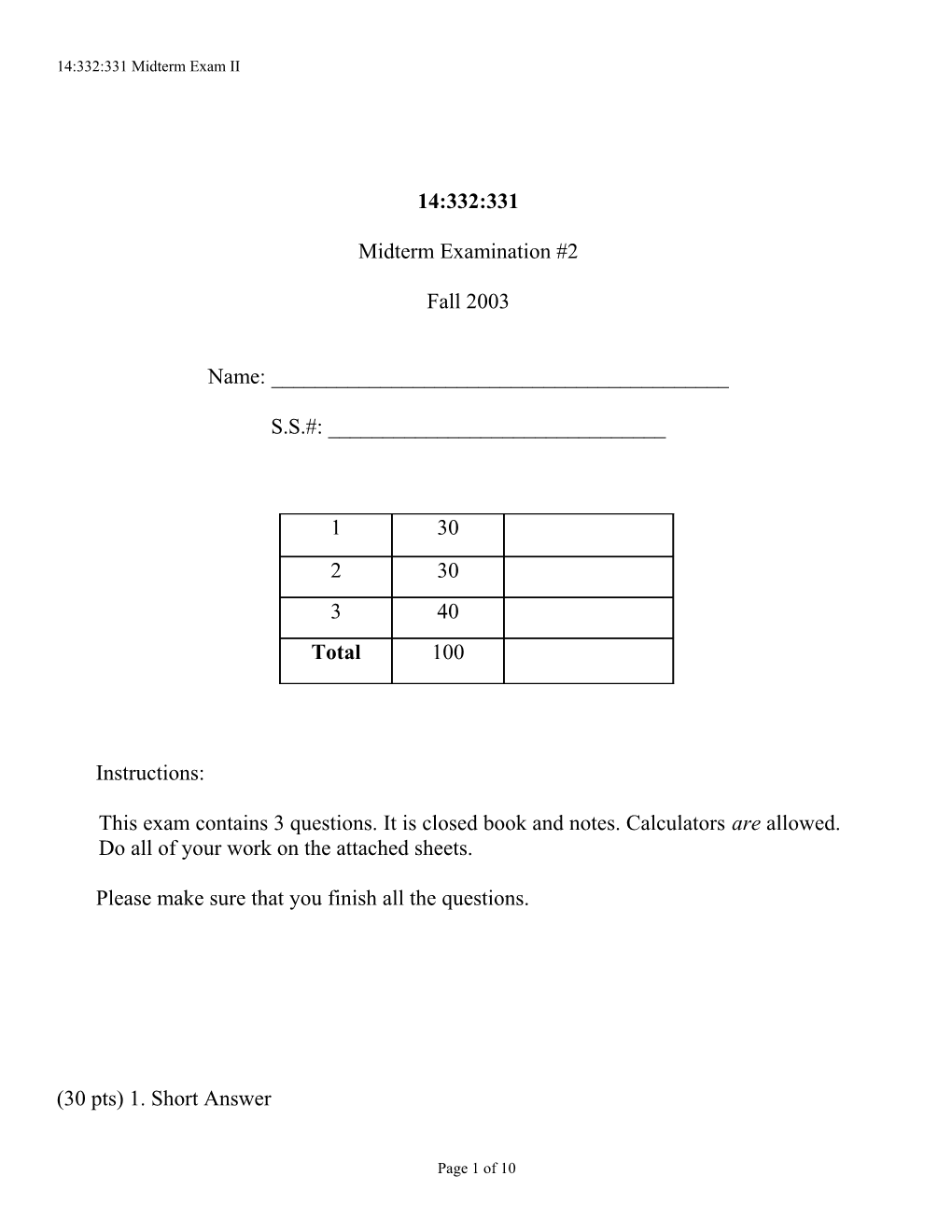

14:332:331

Midterm Examination #2

Fall 2003

Name: ______

S.S.#: ______

1 30 2 30 3 40 Total 100

Instructions:

This exam contains 3 questions. It is closed book and notes. Calculators are allowed. Do all of your work on the attached sheets.

Please make sure that you finish all the questions.

(30 pts) 1. Short Answer

Page 1 of 10 14:332:331 Midterm Exam II

A. (2 pt) Overflow is detected by the hardware according to two conditions. What are these two conditions?

B. (1 pt) What decimal number does this two’s complement binary number represent:

1111 1111 1111 1111 1111 1111 1111 1101two?

C. (2 pt) A negative clock triggered state element is written only in some cycles (not every cycle). Write down the two conditions under which the write operation will take place.

D. (12 pt) Instead of using a special hardware multiplier, it is possible to multiply using shift instructions and add instructions. This is particularly attractive when multiplying by small numbers. In class, we have already looked at the example of how to put 5 times the value of $s2 into $s3 ($s3 $s2*5) ignoring any overflow that may occur by using only add and shift instructions. This question extends that example by putting a small POSITIVE number n into regiester $s1, and then asking you to implement how to put n times the value of $s2 into $s3 ingoring any overflow that may occur ($s3 $s2 * n, where n is in $S1) . In addition to add and shift instructions, you may also want to use logic operations such as AND or OR. PLEASE NOTE THAT THE POSITIVE NUMBER n IS LESS THAN 16. As a reminder the syntax for the MIPS shift left logical (sll) instruction is

sll $t2, $s0, 8 #$t2 = $s0 << 8 bits

Page 2 of 10 14:332:331 Midterm Exam II

E. (13pt) We have a machine that employs a single cycle MIPS datapath. On this datapath, R instructions take 6 ns to complete, lw 8 ns, sw 7 ns, beq 5 ns, and j 2ns. Suppose a program must execute 600 R instructions, 100 lw instructions, 100 sw instructions, 200 beq instructions and 10 j instructions during its execution. What is the total execution time for this program?

In terms of (execution) time, what is the key disadvantage of the sincle cyle MIPS datapath design?

How much time is wasted because of the single cycle MIPS datapath design?

(30 pts) 2. ALU Design

Consider a 4-bit version of MIPS ALU shown on the next page. Here add/subt determines whether an addition (add/subt = 0) or subtraction (add/subt = 1) takes place and op selects the multiplexor output (assume that the top input is selected by an op of 000, etc.). Assume that it takes 2 ns for 2-input and, or gates to settle at their final output

Page 3 of 10 14:332:331 Midterm Exam II

3 ns for a xor gate to settle at its final output 5 ns for a 4-input multiplexor to settle at its final output 4 ns from the latest arriving input for the carry output of a 1-bit full adder to settle at its final output 6 ns from the latest arrivingop input for the sum output of a 1-bit full adder add/subtto settle at its final output A When do the0 result outputs settle at their final values for the inputs shown below (ignoring the test for zero and for overflow)?

result0 add/subt = 0 + outputs settle at tick ______(3 pt) opB =0 01 A = 1010 B = 0011

To what MIPS instruction does this control setting correspond to? (You do not need

to write downA1 the formal instruction, rather, something like A+B will do) ______(1 pt)

When do the result outputs settle at their final values for the inputs shown below result1 (ignoring theB 1test for zero and+ for overflow)?

add/subt0 = 0 outputs settle at tick ______(3 pt) op = 10 A = 0001 B = 0111 zero A To what MIPS2 instruction does this control setting correspond to? (You do not need to write down the formal instruction, rather, something like A+B will do) ______(1 pt) result2 B2 + What is the zero0 output value for this set of inputs? ______(2 pt) Does this operation overflow? ______If so, why; if not, why not? (1 pt)

A3

result3

B3 + 0 Page 4 of 10 overflow 14:332:331 Midterm Exam II

When do the result outputs settle at their final values for the inputs shown below (ignoring the test for zero and for overflow)? add/subt = 1 result settles after ______(3pt) op = 10 A = 0001 B = 0001

Page 5 of 10 14:332:331 Midterm Exam II

To what MIPS instruction does this control setting correspond to? ______(1 pt)

What is the zero output for this set of inputs? ______(2 pt)

Does this operation overflow? ______If so, why; if not, why not? (1 pt)

When do the result outputs settle at their final values for the inputs shown below (ignoring the test for zero and for overflow)? add/subt = 1 result settles after ______(3 pt) op = 11 A = 0000 B = 1000

To what MIPS instruction does this control setting correspond to? ______(1 pt)

What is the zero output for this set of inputs? ______(2 pt)

Assuming that a 4-input nor takes 4 ns to settle to its final output, how long will it take for zero to settle to its correct value assuming worst case inputs and considering all possible operations? (3 pt)

How should the ALU control signals add/subt and op be set when executing a beq instruction? (3 pt)

(40 pts) 3. Single Cycle Datapath Design

Give the settings (making maximum use of don’t cares) for the control signals for the single cycle datapath shown on the next-next page when executing a lw and a j instruction. (For this part of the question ignore the box labeled Barrel Shifter.)

Control lw j Control lw j signal signal

Page 6 of 10 14:332:331 Midterm Exam II

RegDst ALUOp1 Jump ALUOp0 Branch MemWrite MemRead ALUSrc MemtoReg RegWrite

Assuming the following delays for the components in the single cycle datapath PC read access 1 ns memory read access 9 ns register file read 3 ns control logic delay 1 ns ALU delay 4 ns Add delay 3 ns 2x1 mux delay 1 ns

what is the fastest clock speed (i.e., clock cycle time measured from active clock edge to next active clock edge) for the single cycle machine when executing a lw instruction (you may assume that the Sign Extend logic, Shift left 2 logic, PC writes, register file writes, register set up, register hold, and wire delays are all zero)?

What is the fastest clock speed when executing a j instruction?

Your next task is to augment this single cycle MIPS datapath so that it can also perform the shift instructions. The shift instruction have the format

00000 00000 rt rd shamt funct

where the function field is 0 for sll, 2 for srl, and 3 for sra. The barrel shifter can shift the 32-bit input data right (shifting in zero’s for srl or the sign bit for sra) or left (shifting in zero’s) from zero up to 31 bit positions at once. It needs control to tell it how far to shift and what direction/type of shift to perform. Complete both the data inputs and outputs and the control inputs for the barrel shifter

Page 7 of 10 14:332:331 Midterm Exam II

as well as any additional interconnects that need to be made to the augment the datapath. You may only use additional 2-to-1 multiplexors, additional control signals, and additional interconnects. Mark a line that is no longer connected with an

X somewhere along its length where the disconnect should1 occur.0 g e

What new control signal(s) did you need to add and explaina their basic function. d t a R a o e t D

R m d m a e e e M M R a t e a y t s i 1 0 r r s D a c

o e t r e r W a t S m i d r m D e C d e P A M W M 0 1 Give the setting for all the control signals (both previously existing and the one(s) d you added) to execute a sll. l d o r o l r A U e r t e U t L r n e f L i r A z o a h A c B S t 2 f sll sll

Control Signal i Control Signal t f h e S RegDst l MemWrite 0 1 ]

Jump ALUSrc 0 - 5 2 [ r

Branch RegWrite 3 t ] s d 2 d 1

8 n a e a 2 I a c t MemRead a 2 e t i r d e t 3 - r a R n a n S 1 R D e g W 3 D MemtoReg U h i t [ g r L c x 4 S e e n 1 2 A + E ALUOp1 t R a r e r r s C r a l i t d d i d P B 6 p g a d d d ALUOp0 F 1 e A A A D m 8

R u 2 d d e e J t t i i a a t r r e e l s o R R W W D t r i t g ] ] n e ] n t 1 6 2 f

0 U 2 1 o i R t -

- - f ] 0 1 h C 5 5 p 5 0 e 1 S 1 l 1 2 2 [ O [ 1 [ [ ] r r - r r t t t t U 6 s s s s ] 2 L 6 - n n n n 0 I A 2 I I I - 1 5 3 [ 2 r ] [ t r 0 t s - s n 1 I n 3 I [ r n d t y o s d i r t n A I o c u m r e t s s M s n e I d r a d 4 e d R A

Page 8 of 10 C P 14:332:331 Midterm Exam II

Category Instr Op Code Example Meaning Arithmetic add 0 and 32 add $s1, $s2, $s3 $s1 = $s2 + $s3 (R & I add unsigned 0 and 33 addu $s1, $s2, $s3 $s1 = $s2 + $s3 format) subtract 0 and 34 sub $s1, $s2, $s3 $s1 = $s2 - $s3 subt unsigned 0 and 35 subu $s1, $s2, $s3 $s1 = $s2 - $s3 add immediate 8 addi $s1, $s2, 6 $s1 = $s2 + 6 add imm. unsigned 9 addiu $s1, $s2, 6 $s1 = $s2 + 6 Shift sllmultiply 00 andand 024 sllmult $s1, $s1, $s2, $s2 4 $s1hi ||= lo$s2 = $s1<< 4 * $s2 (R srlmultiply unsigned 00 andand 225 srlmultu $s1, $s1, $s2, $s2 4 $s1hi ||= lo$s2 = $s1>> 4 * $s2 format) sradivide 00 andand 326 sradiv $s1, $s2$s2, 4 $s1lo = $s1/$s2,$s2 >> 4 rem. in hi Data loaddivide word unsigned 0 and35 27 lwdivu $s1, $s1, 24($s2) $s2 $s1lo = $s1/$s2,Memory($s2+24) rem. in hi LogicalTransfer storeand word 0 and43 36 swand $s1,$s1, 24($s2) $s2, $s3 Memory($s2+24)$s1 = $s2 & $s3 = $s1 (R(I format) & I loador byte 0 and32 37 lbor $s1,$s1, 25($s2) $s2, $s3 $s1$s1 = =Memory($s2+25) $s2 | $s3 format) loadxor byte unsigned 0 and36 38 lbuxor $s1, $s1, 25($s2) $s2, $s3 $s1$s1 = =Memory($s2+25) $s2 xor $s3 storenor byte 0 and40 39 sbnor $s1,$s1, 25($s2) $s3, $s3 Memory($s2+25)$s1 = !($s2 | $s2) = $s1 loadand upperimmediate imm 1512 luiandi $s1, $s1, 6 $s2, 6 $s1$s1 = =6 $s2* 216 & 6 Page 9 of 10 moveor immediate from hi 0 and13 16 mfhiori $s1$s1, $s2, 6 $s1$s1 = =hi $s2 | 6 movexor immediate from lo 0 and14 18 mfloxori $s1 $s1, $s2, 6 $s1$s1 = =lo $s2 xor 6 14:332:331 Midterm Exam II

Page 10 of 10