Comit Systems, Inc. DES/TDEA (FIPS–46-3) Cryptography Core Fea- tures Product description 1.00

FPGA and ASIC Proven core Core facts Performance 10Mb/s @ 100 Mhz. DES/TDEA (FIPS–46-3) Core Core specifics Fully synthesizable RTL implementation of FIPS 46-3 standard DES/TDEA algorithm Example Device XC2VP-70 CLBs used ~268 Two versions of the core are available Slices used ~1072 o Fully parallel architecture o Sequential implementation Operating Frequency ~100 to 300 MHz Provided with Core Supports DES/TDEA 64 bit encryption & de- cryption Documentation Core Documentation Design File Formats Verilog Source code Key expansion is done inside the core Synthesis Scripts Test Bench Verilog Test bench All three key combinations in TDEA mode Test Vectors All know and random are implemented Design Tool Requirements o K1 = K2 = K3 Xilinx Core Tools P&R tool o K1 != K2 = K3 Entry/Verification Tools Cadence, ModelTech o K1 != K2 != K3 Synthesis Tools Synopsys DC, Synplify Pro. Supports four modes of operation o ECB ASIC Details o CBC Foundry TSMC o CFB o OFB Process 130nm Gate count ~35K Does not require any memory blocks

Descriptor based DMA engine is provided with the core Test vectors include all FIPS published known Generic DMA engine protocol and random test vectors

DMA engine is designed to support data Comit Systems. Inc. provides a Tcl or Verilog fetch, key fetch, ciphered and deciphered based verification models DES/TDEA in ECB, data write back and residue write back func- CBC, CFB, OFB modes of operation tions

DMA engine can be customized for any bus interface protocol

Available in Verilog with extensive verifica- tion suite for functional, post synthesis and post layout verification

1 Comit Systems, Inc.

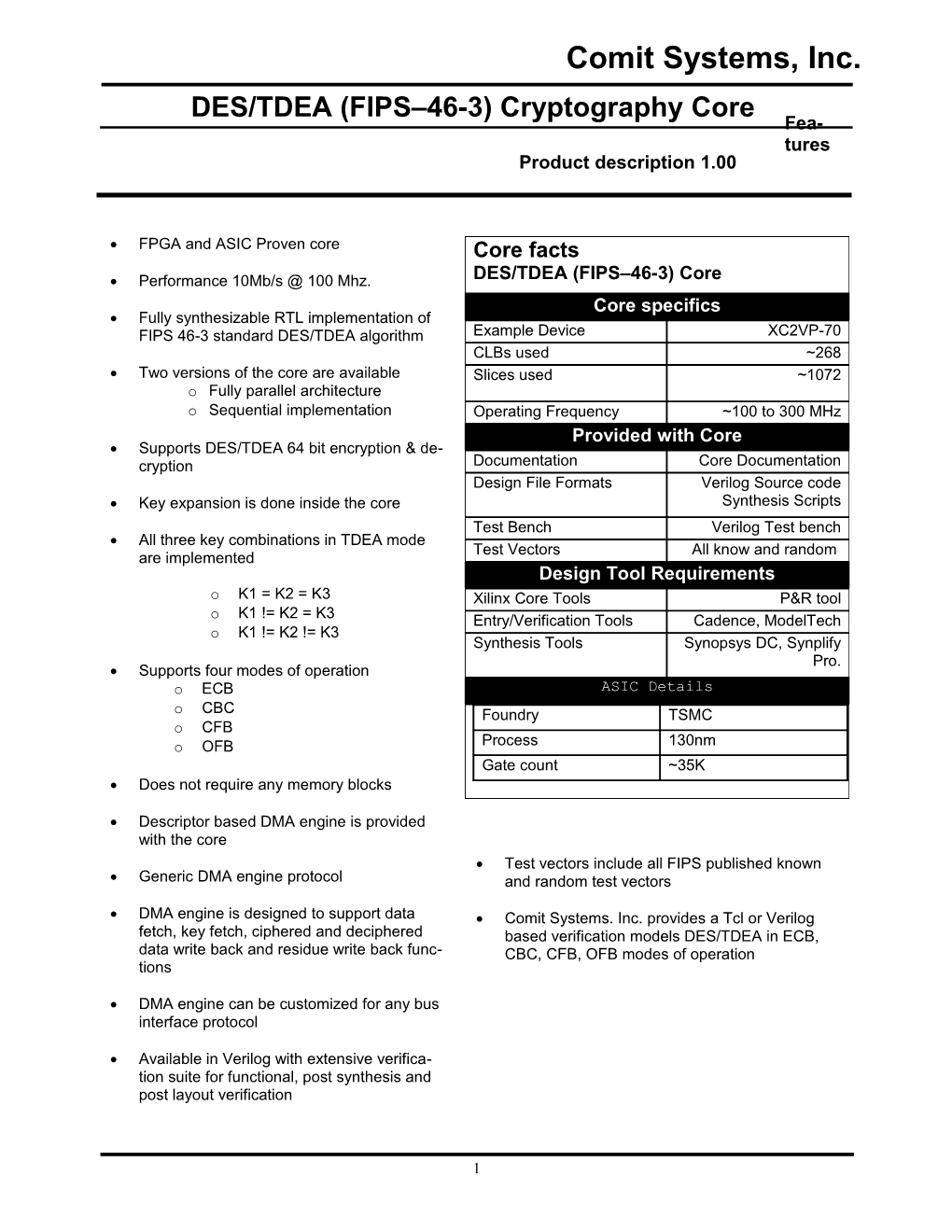

General description Mod-Of-Operation Input Block DES/TDEA cryptography core is one of the cryptography Intellectual property family of Comit Systems. Inc.

Cipher Key Core is implemented in such a way that a single data manipulation block can be used for the low throughput requirements, or a ful-

Round Key K1 ly parallel architecture can be used for the high throughput requirement designs.

This core has been tested on board using Xilinx XC2VP-70, a Virtex II pro family de- vice, and is also silicon proven. Round Key K2 Verification Methods The DES/TDEA cryptography core has been extensively tested using the test bench de- veloped at Comit Systems. This core also has been synthesized and tested on board for Xilinx Virtex II Pro device. Round Key Kn

Round Key Kn

Key Expantion

Comit Systems, Inc. 3375 Scott Blvd. Ste 139 Santa Clara, CA 95054, USA.

Mod-Of-Operation Phone: +1 (408) 988-2988 Input Block URL: http://www.comit.com

FOR MORE INFORMATION CLICK THE Figure 1. DES Core block diagram REQUEST QUOTE LINK ON WEBSITE

2