Due date: November 14, 2001

Department of Computer CS 3402 and Digital Logic 11 Mathematical Sciences Laboratory

Lab 11: A 4-bit Arithmetic-Comparator Device

Objectives:

This lab is designed to extend your knowledge of LogicWorksTM and to introduce you to a controlled logic circuit that performs selection functions depending on the control input.

Background:

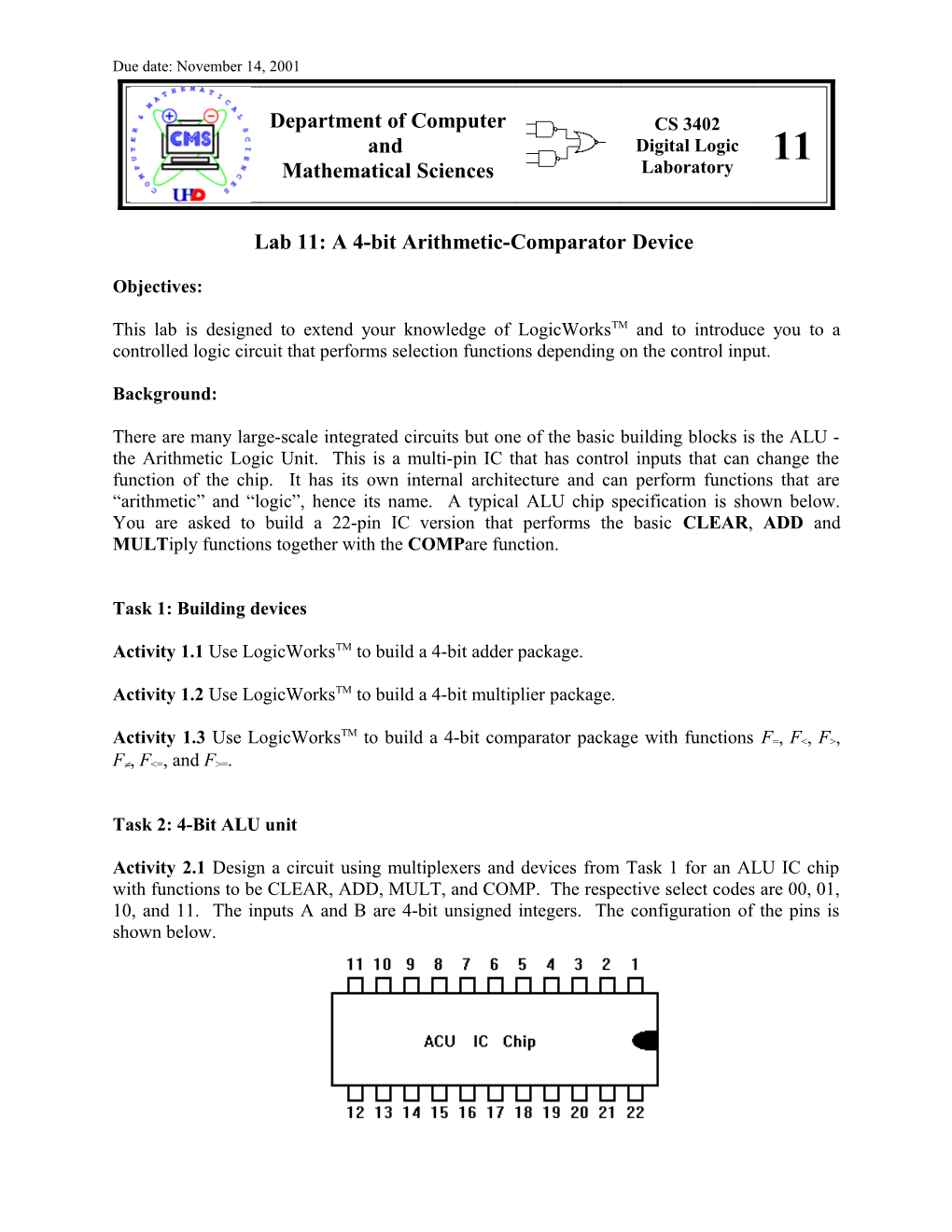

There are many large-scale integrated circuits but one of the basic building blocks is the ALU - the Arithmetic Logic Unit. This is a multi-pin IC that has control inputs that can change the function of the chip. It has its own internal architecture and can perform functions that are “arithmetic” and “logic”, hence its name. A typical ALU chip specification is shown below. You are asked to build a 22-pin IC version that performs the basic CLEAR, ADD and MULTiply functions together with the COMPare function.

Task 1: Building devices

Activity 1.1 Use LogicWorksTM to build a 4-bit adder package.

Activity 1.2 Use LogicWorksTM to build a 4-bit multiplier package.

TM Activity 1.3 Use LogicWorks to build a 4-bit comparator package with functions F=, F<, F>,

F, F<=, and F>=.

Task 2: 4-Bit ALU unit

Activity 2.1 Design a circuit using multiplexers and devices from Task 1 for an ALU IC chip with functions to be CLEAR, ADD, MULT, and COMP. The respective select codes are 00, 01, 10, and 11. The inputs A and B are 4-bit unsigned integers. The configuration of the pins is shown below. Fall 2001, Lab 11, 2

Input pins

Pins 11 and 22 are connected to Gnd and Vcc respectively. Pin 1 is the carry in. Pins 2-5 (A0- A3) are input A (pin 5 is the highest order bit), pins 6-9 (B0-B3) are input B (pin 9 is the highest order bit). Pins 12 and 13 are the select inputs (S0-S1), pin 13 is the higher order bit. Pin 10 is not used and should be marked as NC (not connected).

Output pins

Pins 14 to 21 are to be lettered F0 to F7 respectively. CLEAR sets all F values to 0. For ADD F0-F3 (F3 is the highest order bit) have the output with F4 the carry out. For MULT the output is on F0-F7 with F7 the highest order bit. For COMP F0 indicates equals, F1 indicates not equals, F2 indicates A > B, F3 indicates A B, F4 indicates A < B, and F5 indicates A B.

Activity 2.2 Test your device. Illustrate the device diagram and demonstrate you device.