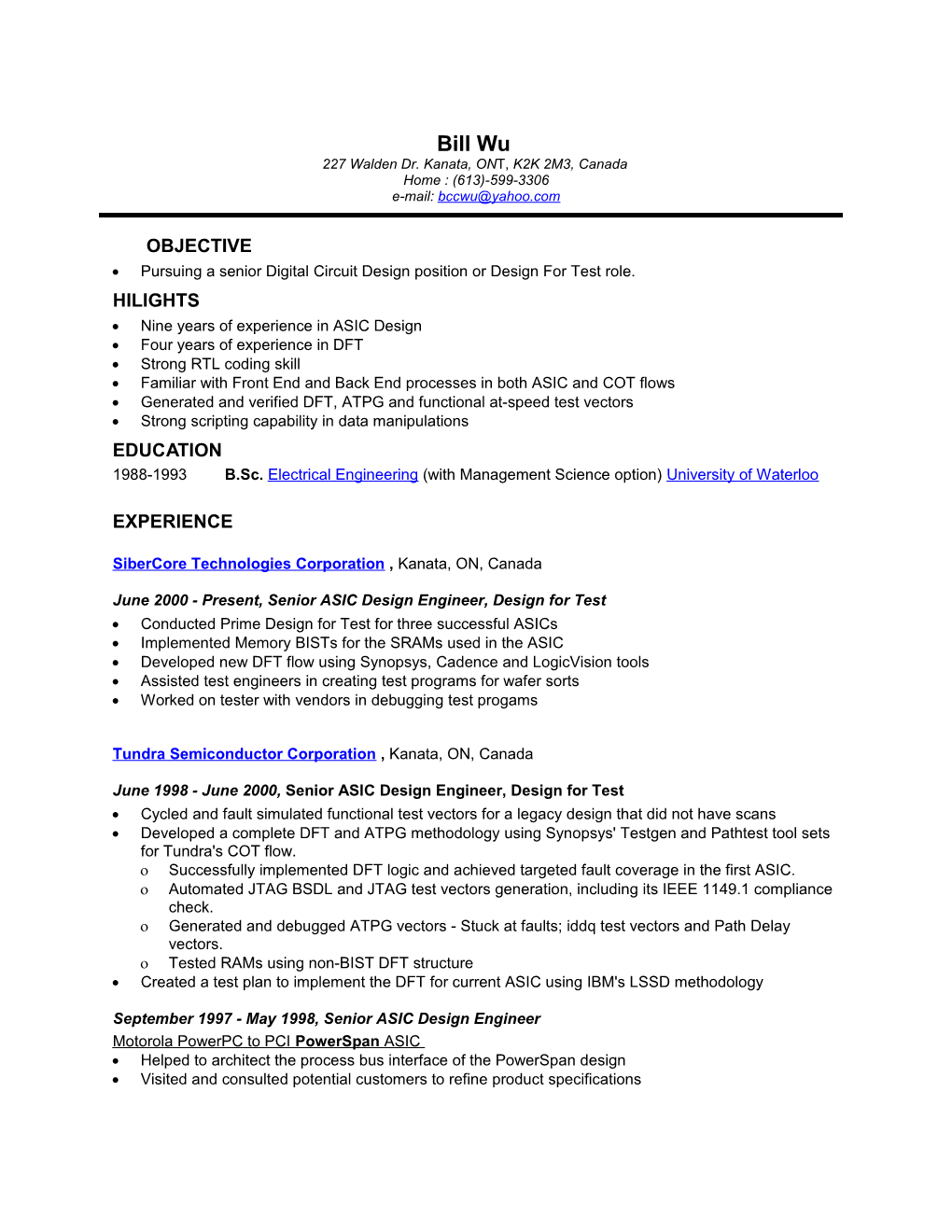

Bill Wu 227 Walden Dr. Kanata, ONT, K2K 2M3, Canada Home : (613)-599-3306 e-mail: [email protected]

OBJECTIVE Pursuing a senior Digital Circuit Design position or Design For Test role. HILIGHTS Nine years of experience in ASIC Design Four years of experience in DFT Strong RTL coding skill Familiar with Front End and Back End processes in both ASIC and COT flows Generated and verified DFT, ATPG and functional at-speed test vectors Strong scripting capability in data manipulations EDUCATION 1988-1993 B.Sc. Electrical Engineering (with Management Science option) University of Waterloo

EXPERIENCE

SiberCore Technologies Corporation , Kanata, ON, Canada

June 2000 - Present, Senior ASIC Design Engineer, Design for Test Conducted Prime Design for Test for three successful ASICs Implemented Memory BISTs for the SRAMs used in the ASIC Developed new DFT flow using Synopsys, Cadence and LogicVision tools Assisted test engineers in creating test programs for wafer sorts Worked on tester with vendors in debugging test progams

Tundra Semiconductor Corporation , Kanata, ON, Canada

June 1998 - June 2000, Senior ASIC Design Engineer, Design for Test Cycled and fault simulated functional test vectors for a legacy design that did not have scans Developed a complete DFT and ATPG methodology using Synopsys' Testgen and Pathtest tool sets for Tundra's COT flow. Successfully implemented DFT logic and achieved targeted fault coverage in the first ASIC. Automated JTAG BSDL and JTAG test vectors generation, including its IEEE 1149.1 compliance check. Generated and debugged ATPG vectors - Stuck at faults; iddq test vectors and Path Delay vectors. Tested RAMs using non-BIST DFT structure Created a test plan to implement the DFT for current ASIC using IBM's LSSD methodology

September 1997 - May 1998, Senior ASIC Design Engineer Motorola PowerPC to PCI PowerSpan ASIC Helped to architect the process bus interface of the PowerSpan design Visited and consulted potential customers to refine product specifications [email protected] (613) 599-3306 Page 2 of 3 QSPAN1.2 ASICs Improved performance and fixed bugs in Performed Static Timing Analyses Optimized ECOs and timing using Cadence CELL3 Used Chrysalis to ensure synthesis correctness and ECOs Analyzed SSN effects on the PADs' AC timings

December 1995 - August 1997, Intermediate ASIC Design Engineer Motorola MPC860/360/040 to PCI QSPAN QSPAN1.1 ASICs Designed the Motorola slave bus interface for QSPAN Developed a sophisticated two-pass synthesis Synopsys script Verified the internal DMA channel Generated manufacturing test vectors

June 1993 - November 1995, Junior ASIC Design Engineer - Futurebus+ LIFE bus bridge ASIC Integrated multiple Verilog testbenches into one unified testbench Created stimuli to increase functional verification coverage Interfaced with National Semiconductors Corp. for design sign off and ECOs Verified hardware and debugged evaluation card in the production PCI-VME UNIVERSE ASIC Maintained and improved part of the VME bus interface design Developed Synopsys' synthesis script Modified the functional testbench and its stimuli to produce regenerative manufacturing test vectors

September 1988 - May 1993, Co-op Student Computing Devices Company Redesigned and debugged single board computer from Z8000 based to MC68020 Evaluated the performance of R3000 and R4000 family microprocessors Designed and conducted the Touchscreen Experiment and analyzed the results Ontario Hydro Developed Pascal programs and macros to automate data manipulations Programmed Relational Database using SQL for report generations Lumonics Inc. Simulated UV Corona discharge inside a new Excimer laser LANGUAGE & TOOLS Hardware descript language: Verilog Synthesis tools: Synopsys Design Compiler and Test Compiler; Cadence's Ambit. Verification tools: Cadence Verilog and its variants Formal verification: Chrysalis DFT and ATPG tools: Synopsys' Testgen and Pathtest and TetraMAX; Mentor Graphics' Fastscan; LogicVision DFT tool set Device simulation tool: PSpice Layout tool: Cadence Cell3 Scripting tools: AWK, Perl, sed and tcl/tk Programming Language: C, SQL, Pascal, Motorola MC68K and PowerPC assembly languages. Operating Systems: UNIX, Windows 95 and MAC OTHER INFORMATION Bilingual: English/Chinese Citizenship: Canadian [email protected] (613) 599-3306 Page 3 of 3