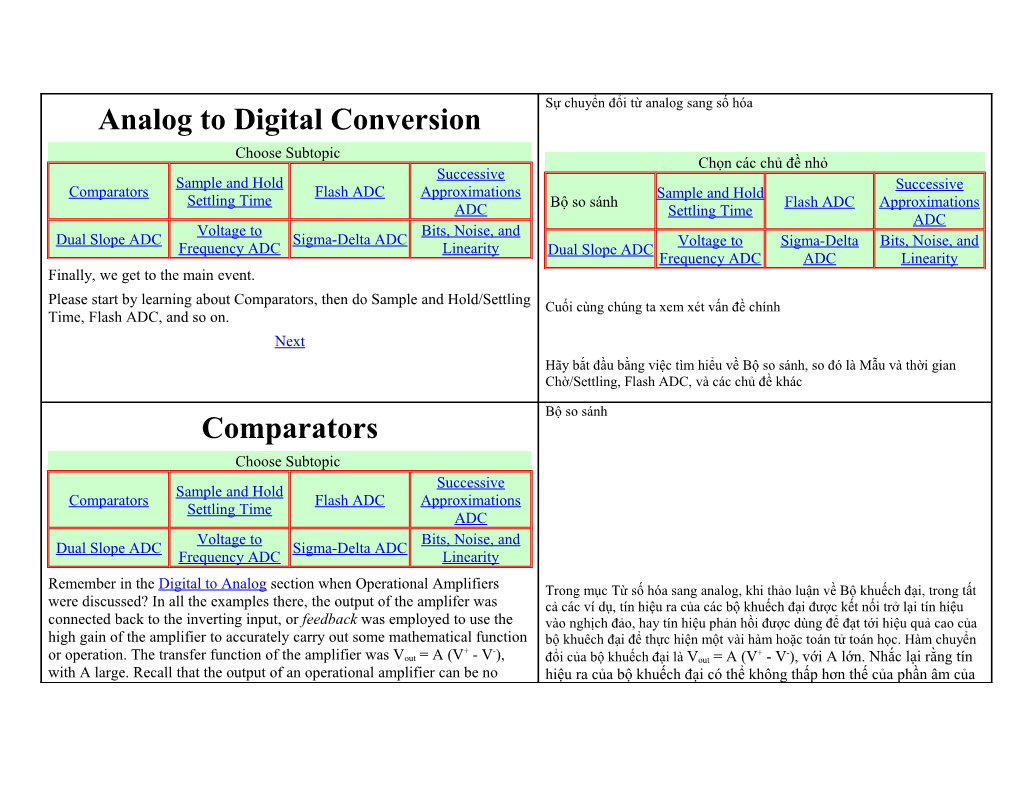

Sự chuyển đổi từ analog sang số hóa Analog to Digital Conversion Choose Subtopic Chọn các chủ đề nhỏ Successive Sample and Hold Successive Comparators Flash ADC Approximations Sample and Hold Settling Time Bộ so sánh Flash ADC Approximations ADC Settling Time ADC Voltage to Bits, Noise, and Dual Slope ADC Sigma-Delta ADC Voltage to Sigma-Delta Bits, Noise, and Frequency ADC Linearity Dual Slope ADC Frequency ADC ADC Linearity Finally, we get to the main event.

Please start by learning about Comparators, then do Sample and Hold/Settling Cuối cùng chúng ta xem xét vấn đề chính Time, Flash ADC, and so on. Next Hãy bắt đầu bằng việc tìm hiểu về Bộ so sánh, so đó là Mẫu và thời gian Chờ/Settling, Flash ADC, và các chủ đề khác

Bộ so sánh Comparators Choose Subtopic Successive Sample and Hold Comparators Flash ADC Approximations Settling Time ADC Voltage to Bits, Noise, and Dual Slope ADC Sigma-Delta ADC Frequency ADC Linearity

Remember in the Digital to Analog section when Operational Amplifiers Trong mục Từ số hóa sang analog, khi thảo luận về Bộ khuếch đại, trong tất were discussed? In all the examples there, the output of the amplifer was cả các ví dụ, tín hiệu ra của các bộ khuếch đại được kết nối trở lại tín hiệu connected back to the inverting input, or feedback was employed to use the vào nghịch đảo, hay tín hiệu phản hồi được dùng để đạt tới hiệu quả cao của high gain of the amplifier to accurately carry out some mathematical function bộ khuêch đại để thực hiện một vài hàm hoặc toán tử toán học. Hàm chuyển + - + - or operation. The transfer function of the amplifier was Vout = A (V - V ), đổi của bộ khuếch đại là Vout = A (V - V ), với A lớn. Nhắc lại rằng tín with A large. Recall that the output of an operational amplifier can be no hiệu ra của bộ khuếch đại có thể không thấp hơn thế của phần âm của lower than the potential coming from the negative side of the power supply nguồn điện và cũng không thể cao hơn thế của phần dương của nguồn nor can it be higher than the positive side of the supply (there are engineering ( Các chi tiết kỹ thuật ……………., nhưng đừng để các chi tiết đó làm details that prevent going to exactly the "power supply rails," but don't let mờ đi bức tranh lớn). Giả sử một máy khuếch đại đang chạy với một those details obscure the big picture). Suppose an operational amplifier is run nguồn điện +5V (Nguồn âm cung cấp 0V). on a +5 V power supply (negative supply provided by 0 V). 1) Điện thế nhỏ nhất có thể nhận được là bao nhiêu? (click shows answer, mouse exit from button hides answer) 2) Điện thế cao nhất có thể nhận được là bao nhiêu? 1) What is the lowest output potential possible? 3) Nếu V+ = 2.00 V và V- = 1.99 V với A = 104 , điện thế nhận được sẽ là bao nhiêu? 4) Nếu V+ = 2.00 V và V- = 2.01 V với A = 104, Điện thế nhận được 2) What is the highest output potential possible? sẽ là bao nhiêu?

3) If V+ = 2.00 V and V- = 1.99 V with A = 104, What will the output potential be? 4) If V+ = 2.00 V and V- = 2.01 V with A = 104, What will the output potential be?

A comparator is thus a 1 bit analog to digital converter. If the input to the non-inverting input is greater than that to the inverting input, the output is a logical 1. If the input to the non-inverting input is less than that to the inverting input, the output is a logical 0. We thus have the key element for asking "is the signal above or below a threshold level?" We will use comparators in EVERY analog-to-digital converter to detect analog thresholds. Next Vì thế một bộ so sánh là một máy chuyển đổi tín hiệu 1bit. Nếu tín hiệu vào chưa nghịch đảo lớn hơn tín hiệu vào nghịch đảo, tín hiệu ra là 1. Nếu tín hiệu vào không nghịch đảo nhỏ hơn tín hiệu vào nghịch đảo, tín hiệu ra là 0. Do đó chúng ta có một yếu tốt quan trọng để đặt ra câu hỏi “ Tín hiệu ở trên hay dưới ngưỡng?” Chúng ta sẽ sử dụng bộ so sánh trong tất cả các máy chuyển đổi để tìm ra các ngưỡng analog. Sample and Hold Settling Time Choose Subtopic

Successive Sample and Hold Comparators Flash ADC Approximations Settling Time ADC

Voltage to Bits, Noise, and Dual Slope ADC Sigma-Delta ADC Frequency ADC Linearity

Sample and Hold Circuit "Time is what keeps everything from happening at once." If we want to measure a signal, we can not ignore the fact that it changes with time. There are several approaches to dealing with this. We could measure the signal very fast, do it many times, and after we're done figure out what the right time scale would have been. We could average the signal. Or we can snatch the value of the signal, hold that value steady, and digitize the single, sampled value at our leisure. A sample and hold circuit (or its first cousin, track and hold) can be employed with digitizers to pluck a single value from an analog source, keep that value stable for at least the time required for digitization, and can then be set to grab (sample) a value at a later time. Thời gian ổn định mạch lấy mẫu và giữ Consider the following circuit: Mạch lấy mẫu và giữ "Thời gian làm cho mọi việc khồn cùng xảy ra một lúc." Nếu muốn đo If the switch is closed, the capacitor is charged to the potential V . When the in một tín hiệu, không thể quên là nó thay đổi theo thời gian. Có nhiều switch opens, the capacitor holds its charge, so the follower op amp has an cách giải quyết vấn đề này. Đo rất nhanh, đo nhiều lần, từ đó dự đoán output potential of what potential was on the capacitor at the moment the được thang thời gian thích hợp. Ta cũng có thể lấy trung bình tín hiệu. switch opened. If the switch is typically closed, but opens momentarily when Hoặc cũng có thể chớp lấy giá trị của tín hiệu, giữ giá trị đó và số hóa we want to make a measurement, this is a track and hold circuit. If we chúng. Một mạch điện lấy mẫu và cố định có thể được dùng với thiết typically leave the switch open, but momentarily close it when we want to bị số hóa để đọc lấy một giá trị duy nhất từ nguồn analog, giữ giá trị grab a measurement, it is a sample and hold circuit. đó trong ít nhất là khoảng thời gian đủ để số hóa, và sau đó có thể This sounds too easy. Time for a reality check. được dùng để chớp( lấy mẫu) một giá trị. Xem mạch điện sau: Settling Time for Sample and Hold The potential which we sample comes from some source with non-zero Nếu công tắc được đóng, tụ điện được nạp tới điện thế V . Khi công internal resistance. We thus recognize that, when the switch is closed, we are in tắc mở, tụ điện giữ điện tích của nó, nên dòng điện có điện thế của looking at an RC circuit. The capacitance is obvious -- it's the C in the circuit. điện thế trên điện dung vào thời điểm mở công tắc.Nếu công tắc đóng, What about the R? The output resistance of typical operational amplifiers is nhưng mở tức thời khi ta muốn thực hiện phép đo, đây là một mạch between 1 Ω and 1000 Ω. If we always put a buffer amplifer before the điện bám và giữ. Nếu thường để công tắc mở, nhưng đóng lại đột ngột switch, then the RC time constant for this circuit is between C seconds and để lấy số liệu, nó là một mạch điện lấy mẫu và giữ. 1000C seconds, with C in Farads. Review time! Fill in the following table. What is the RC time constant for each combination Thời gian ổn định cho mạch lấy mẫu và giữ of R and C? Điện thế ta lấy mẫu là từ nguồn có điện trở trong khác 0. Bởi vậy, khi Click here for Answers 1 pF 1 nF 1 μF công tắc đóng, có mach điện RC Điện dung hiển nhiên là C. Còn R thí sao? Điện trở ngoài của bộ khuyếch đại là giữa 1 Ω và 1000 Ω. Nếu ta 1 Ω luôn thêm bộ khuyếch tán đệm trước khi chuyển công tắc, thì hằng số thời gian RC cho mạch điện này là giữa khoảng C giây và 1000C giây, 10 Ω theo C in Farads. Điền vào bảng. Hằng số thời gian cho mỗi tổ hợp R và C la gì 100 Ω Click here for 1 pF 1 nF 1 μF 1000 Ω Answers

From this, we see that the rate of response can vary over many orders of 1 Ω magnitude. The lower the capacitance, the less charge is needed to represent a given potential, but the greater the influence of shot noise on the 10 Ω measurement. 1 V stored on 1 pF is about 16 million electrons, which has an uncertainty of 1 part in 4000. Such a small capacitor is inappropriate for even 100 Ω a 12 bit converter, much less something with greater resolution. 1 V stored on 1 μF is about 1.6 × 1012 electrons, with an uncertainty of 1 part in 4 × 106, 1000 Ω about the resolution of a 24 bit converter. To think about: even without any knowledge of the inside workings of an Từ đây, nhận thấy, tốc độ phản hồi có thể biến thiên theo nhiều độ lớn. analog-to-digital converter, why will high resolution conversions always be Điện dung càng thấp, càng ít điện tích cần thiết để biểu diễn một điện slower then low-resolution conversions? Click for answer thế nhưng phép đo lại càng bị ảnh hưởng bởi nhiễu ngắn. 1 V chứa trong 1 pF gồm 16 triệu electron, nhưng có độ bất định là 1/4000. Tụ điện nhỏ như vậy không thích hợp với kể cả bộ chuyển đổi 12 bit, Ignoring all nonidealities, recall that it takes longer than one RC time càng không thể cho độ phân giải tôt hơn.. 1 V chứa trong 1 μF gồm constant to accurately reach a steady state voltage on a capacitor. Let's do 12 6 1.6 × 10 electron, với độ bất định là 1 /( 4 × 10 _), bằng độ phân giải -t/RC another exercise. Recall that Vcap = Vstep(1-exp ). So let's figure out how của bộ chuyển đổi 24 bit. long it takes to get the accuracy of a sample and hold circuit to some number of bits. We already worked problems like this in the section on digital to Suy nghĩ: Ngay cả khi không có chút hiểu biết gì về cấu tạo bên trong analog conversion. của chuyển đổi analog-số, tại sao bộ chuyển đổi phân giải cao luôn chậm hơn chuyển đổi phân giải thấp? Ấn xem câu trả lời. If RC = 1 μs, how long must the sampling switch for the sample and hold stay closed to get the capacitor charged adequately for 16 bit accuracy? Click for Bỏ qua tất cả các điều kiện không lý tưởng, nhớ lại rằng phải mất nhiều hằng số thời gian để đạt được chính xác hiệu điện thế ổn định answer - trên tụ điện. Hãy làm một ví dụ khác, nhớ rằng Vtụ = Vtừng bước(1-exp t/RC). Vậy hãy xem xem phải mất bao lâu để đạt được độ chính xác của A track and hold does not see jumps in input as often as a sample and hold, so mạch lấy mẫu và giữ tới vài con số của bit. Ta đã làm các bài tập if there are long pauses between taking samples, a track and hold reaches high tương tự trong phần chuyển đổi số-analog. precision more quickly than a sample and hold. Because it is easy to signal Nếu RC = 1 μs, phải mất bao lâu để công tắc mẫu của mạch lấy mẫu average a long list of numbers, it has become common to take data very fast, và giữ gần với tụ được tích điện phù hợp với độ chính xác 16 bit. Ấn then average or take subsets of the data for emulating infrequent xem trả lời. measurements. Thus, sample and hold is more common than track and hold. Một mạch bám và giữ không có các bước nhảy đầu vào như trong Unfortunately, there are non-idealities, so just dealing with RC time constants mạch lấy mẫu bởi vậy nếu có thời gian nghỉ dài giữa các lần lấy mẫu, is over-optimistic. The switch does not turn on or turn off instantaneously. thì mạch bám và giữ cho kết quả chính xác hơn so với mạch lấy mẫu There is some resistance associated with the switch when it is on, and some và giữ. stray capacitance when it is off. During switching, there are noise spikes or glitches. Thus, after the switch opens, one must wait some period (usually Bởi việc lấy trung bình tín hiệu của một dãy số dài tương đối dễ, nên less than 1 μs) before starting digitization. Given the numbers in the last nói chung thường lấy dữ liệu rất nahnh, rồi lấy trung bình hoặc lấy tập problem above, it is little wonder that typical 16 bit analog to digital con của các số liệu để tiến hành các phép đo mô phỏng không thường conversion for many years was limited to 50 to 100 kHz. In recent years, xuyên. Bởi vậy mạch lấy mẫu và giữ phổ biến hơn mạch bám và giữ. conversion rates over 1 MHz have become common. What led to the change? Không may là các điều kiện không lý tưởng có tồn tại, nên việc giải Low resistance switches with few glitches, and the smallest possible quyết vấn đề về các hằng số thời gian RC đã được đánh giá hơi quá lạc capacitors. quan.Công tắc không tắt và bật tức thì. Trong lúc chuyển công tắc, có Next nhiễu. Vì thế, sau khi công tắc mở, phải đợi một thời gian( thường it hơn μs) trước khi tiến hành số hóa. before starting digitization. Theo các số liệu cho trong ví dụ cuối cùng ở trên, không lạ là chuyển đổi thong thường 16 bit từ analog sang số đã bị giới hạn trong nhiều năm từ 50 tới 100 kHz. Trong những năm gần đây, tốc độ chuyển đổi hơn 1 MHz đã trở nên bình thường. Điều gì làm nên thay đổi đó? Công tắc điển trở thấp với ít nhiễu và tụ điện nhỏ nhất có thể.

Flash Analog to Digital Conversion Choose Subtopic Successive Sample and Hold Comparators Flash ADC Approximations Settling Time ADC Voltage to Bits, Noise, and Dual Slope ADC Sigma-Delta ADC Frequency ADC Linearity The first type of analog to digital coverter (henceforth, ADC) we will consider is the fastest: the aptly-named flash converter. This converter uses comparators to determine what potential is instantaneously present on an input, and just as instantaneously to provide a digital output instantaneously reporting the value. No sample and hold is employed. To keep the situation simple, let's design a 2 bit straight binary flash converter. The output codes can be 00, 01, 10, or 11. If the full range of the converter is 5 V, then the transitions between the codes should be at 1/4, 1/2, and 3/4 of full scale or 1.25 V, 2.5 V, and 3.75 V. If the instantaneous Chuyển đổi Flash từ Analog sang Digital potential is, say, 1.35 V, the output should be 01. We can generate the reference potentials with a resistive divider, and use one comparator for each Loại đầu tiên của chuyển đổi analog sang số (ADC) mà ta sẽ xem xét reference level. That means the analog section of the circuit looks like this: là loại nhanh nhất: có tên đúng với đặc điểm nhanh của nó là chuyển đổi flash (chớp). Chuyển đổi này dùng các máy so mẫu để xác định điện thế nào có mặt tức thời trên đầu vào, và tức thời cung cấp một The switching speed is the speed of the comparators, and that can be đầu ra số thong báo giá trị. Không dùng mạch lấy mẫu và giữ nào. extremely fast as long as the input capacitance of the comparators is small. Để đơn giản vấn đề, hãy thiết kế một chuyển đổi flash 2bit nhị phân There are 3 comparators, the outputs of which need to be encoded into 2 bits. chuẩn. Mã hóa đầu ra có thể là 00, 01, 10, or 11. Nếu thang đầy đủ của The most significant bit (MSB) gets set to 1 as long as the signal is at least chuyển đổi là 5 V thì chuyển tiếp giữa các mã hóa là ở 1/4, 1/2, và 3/4 2.5 V, while the least significant bit (LSB) gets set if either the 3.75 V của thang đo đầy đủ hay 1.25 V, 2.5 V, và 3.75 V. Nếu giả sử điện thế comparator output is positive or the 1.25 V comparator is ON and the 2.5 V tức thời là 1.35V, thì đầu ra sẽ là 01. Ta có thể tạo ra các điện thế gốc comparator is OFF. Adding logic gates (the pointed output gate is OR, the với bộ chia điện trở, và sử dụng một máy so mẫu cho mỗi mức qui rounded end is AND, and a small circle indicates logical NOT), the full chiếu. Có nghĩa là phần analog của mạch sẽ giống thế này: circuit is:

To get an encoding of 4 output levels, we required 3 comparators. How many comparators would we need for 256 output levels (8 bits)? See the answer

As the number of comparators increases, one rapidly reaches a point of diminishing returns. Every time one wishes to add one more bit to the ADC output, one doubles the number of comparators. Since each comparator has some input capacitance (and the wiring feeding the comparators has capacitance as well!), the maximum speed drops because RC increases. This collides with the greater settling time needed to improve the number of bits of accuracy. Thus, beyond 8 bits, flash converters face severe limitations. Nevertheless, in the fastest digital instruments, in high speed cameras, and in communications systems, digitization rates of over 1 GHz have been realized, while several hundred MHz digitization is routine. Using the arguments we have already made, assuming a source resistance of 50Ω (quite common), input capacitance for each comparator of 1 pF, and ignoring speed limitations Tốc độ chuyển đổi là tốc độ của các máy so mẫu, và có thể rất nhanh in the comparator (dream on!), the fastest a flash converter can digitize is: nếu điện dung đặt vào các máy so mẫu là nhỏ. Number of Maximum Digitization Có 3 máy so mẫu, đầu ra của chúng cần được mã hóa thành 2 bit. Cho bits Rate (Hz) đến khi tín hiệu nhỏ nhất vẫn là 2.5 V thì bit quan trọng nhất khởi 1 29 GHz động 1, trong khí đó bit ít quan trọng nhất được khởi động nếu đầu ra 4 1.8 GHz của máy so 3.75 V là dương hoặc máy so 1.25 V đang mở và máy 2.5 8 450 MHz V đang đóng. Cộng thêm cổng logic ( cổng đầu chĩa ra là OR, cổng có 12 200 MHz đầu tròn là AND và một vòng tròn nhỏ biểu hiện logic NOT), mạch 16 113 MHz đầy đủ: Let's critically consider this table. Silicon transistors can not switch at 29 GHz; the fastest switches can run at less than 10 GHz. GaAs can reach 30 GHz, but is not commonly used in consumer electronics. For the highest numbers of bits (>8), there is an additional error source that we haven't yet considered. A flash converter is no more accurate than the resistors in the divider chain. To be useful, a 16 bit converter needs the divider chain to be accurate to 1 part in 65536. The best resistors one can purchase are ~ 0.01% accurate at a single temperature (and change resistance by 5 parts per million per degree Celsius). 0.01% is about 12 bit resolution. This hints at a more general problem: high resolution simply can't count on precision of resistors to set digitization precision. We ill find that some of the other ADC designs depend on component precision, others not. Next Để tạo một mã hóa 4 mức, cần có 3 máy so mẫu. Vậy cần bao nhiêu máy so mẫu để có 256 mức đầu ra (8bit)? Xem trả lời. Khi số máy so mẫu tăng lên, ta nhanh chóng gặp phải điểm suy giảm. Cứ khi cố cộng thêm 1 bit vào đầu ra ADC, thì lại phải gấp đôi số máy so.Do mỗi máy có điện dung nào đó (và dây dẫn của máy so cũng có điện dung), tốc độ cực đại giảm vì RC tăng. Điều này mâu thuẫn với thời gian ổn đinh lớn để cải thiện số bit chính xác. Vì thế, ngoài vấn đề về 8 bit, các bộ chuyển đổi còn có những giới hạn khác. Tuy nhiên, trong các thiết bị nhanh nhất, như máy ảnh tốc độ cao, và trong thong tin lien lạc, tốc độ số hóa 1 GHz đã đạt được, trong khi cỡ vài trăm MHz là thong thường. Dùng các điểm mà ta đã tổng kết được, giả sử có một điện trở nguồn 50Ω (khá phổ biến), điện dung đầu vào cho mỗi máy so mẫu là 1pF, và bỏ qua các giới hạn về tốc độ trong máy so mẫu( lý tưởng), tốc độ số hóa nhanh nhất của bộ chuyển đổi flash có thể Tốc độ số hóa nhanh nhất Số bit (Hz) 1 29 GHz 4 1.8 GHz 8 450 MHz 12 200 MHz 16 113 MHz Xem xét kĩ bảng này. Các transitor silicon không thể chuyển ở 29 GHz, chuyển nhanh nhất có thể là nhỏ hơn 10 GHz. GaAs có thể đạt tới 30 GHz, nhưng không thường được sử dụng trong điện tử dân dụng. Với số lượng bit nhiều nhất (>8), có thêm nguồn gây sai số trong chuỗi bộ chia. Để có lợi nhất, bộ chuyển đổi 16 bit cần chuỗi bộ chia chính xác tới1/65536. Điện trở tố nhất có thể mua có độ chính xác tới 0.01% ở một nhiệt độ (và điện trở thay đổi mỗi 5/triệu độ C). 0.01% vào khoảng 12 bit phân giải. Điều này lien quan tới một vấn đề tổng quát hơn: để đạt được sự chính xác số hóa, độ phân giải cao không phụ thuộc một cách đơn giản chỉ vào độ chính xác của điện trở. Ta cũng tìm được một vài thiết kế ADC khác phụ thuộc vào các yếu tố chính xác khác, một số khác thì không.

Successive Approximations ADC Choose Subtopic Successive Sample and Hold Comparators Flash ADC Approximations Settling Time ADC Voltage to Bits, Noise, and Dual Slope ADC Sigma-Delta ADC Frequency ADC Linearity From the time of their invention in the 1940s until the turn of the 21st Century, Successive Approximation ADCs were the most common choice for high resolution, low cost, intermediate speed digitization. They remain popular except for the very highest resolution digitization. It is CRITICAL that a sample and hold stage precede a successive approximations converter! As we will see, the sampled signal must be stable for the entire duration of a conversion. A successive approximations ADC has much in common with the children's classic, "The Story of the Three Bears." At each stage of the story, results are too hot, too cold, or just right, too big, too small, or just right, etc. Because measurements are hardly ever "just right" (due to noise), a guess at an answer ADC lấy gần đúng liên tiếp to any question will likely be too high or too low. So if one starts making large amplitude guesses, then takes progressively smaller steps, one will Từ khi nó được phát minh vào những năm 1940 cho đến đầu thế kỉ 21, always be too high or too low, but will iterate to "very close to just right." ADC lấy gần đúng lien tiếp là lựa chọn phổ biến nhất để có được độ phân giải cao, giá thành thấp, tốc độ số hóa vừa phải. Trừ chiếc máy The key here is that we synthesize a voltage using a DAC, compare the số hóa phân giải cao nhất ra thì chúng vẫn còn phổ biến. DAC's output voltage to the signal input voltage, then increase or decrease the DAC's output until the code feeding the DAC gives the closest possible Điều quan trọng là một giai đoạn lấy mẫu và giữ được tiến hành trước match to the potential of the input signal. For the simplest possible example, bước chuyển đổi lấy gần đúng lien tiếp. Như sẽ thấy, tín hiệu được lấy let's use a 1 bit DAC. The full scale signal will be +5 V, and 0 will sẽ phải ổn định trong suốt quá trình chuyển đổi. correspond to 0. Thus, if the input is over +2.5 V, the output should be with Một ADC lấy gần đúng lien tiếp có nhiều điểm chung với câu chuyên the DAC's bit set. Otherwise, the DAC output should be 0. How do we trẻ con cũ “Câu chuyện về 3 chú gấu”. Ở mỗi giai đoạn của câu proceed? chuyên, các kết quả là quá nóng, quá lạnh, vừa phải, quá to, quá nhỏ, 1) Trigger the sample and hold to hold the input value. hay vừa phải... Do các phép đo khó mà lấy “ vừa phải” được (do nhiễu), ta cũn có thể đoán được câu trả lời cho bất kì câu hỏi nào cũng 2) Guess that the digitized value is 1. Feed that logical 1 to a 1 bit DAC dễ sẽ là “quá cao, hay quá thấp”. Nếu bắt đầu thực hiện nhiều phép which puts out 1/2 of the ADC's full range, or +2.5 V. đoán biên độ, rồi lấy từng nấc các bước nhỏ hơn, ta có thể luôn ở trạng 3) Use a comparator to look at the DAC output and the held signal from the thái “quá cao hay quá thấp” nhưng sẽ lặp lại “về phía bên phải”. sample and hold. If the sampled value is ≥ 2.5 V, the comparator output will Vấn đề ở đây là, ta tạo ra một hiệu điện thế bằng DAC, so sánh với các be high. If the sampled value is < 2.5 V, the comparator output will be low. hiệu điện thế đầu ra của DAC với hiệu điện thế đầu vào tín hiệu, rồi 4) If the comparator output is high, the digitized value is 1; otherwise, the tăng hay giảm đầu ra DAC cho đến khi mã cung cấp cho DAC phù single bit is too big to represent the input signal, so we set it back to 0 and hợp nhất với điện thế của tín hiệu đầu vào.Ví dụ đơn giản nhất có thể, we're done. dùng DAC 1 bit.Tín hiệu đầy đủ sẽ là +5V, và 0 sẽ tương ứng với 0. A picture may help: Vì thếm nếu đầu vào là +2.5, đầu ra sẽ cặp với các bit của DAC. Nếu không, đầu vào DAC sẽ bằng 0. Tiếp theo, lam như sau: 1) Khởi động mẫu và giữ giá trị đầu vào Note that if the DAC output is greater than the sample and hold output, the comparator output is high, while if the DAC output is lower than the sampled 2)Đoán răng giá trị được số hóa là 1. value, the comparator output is low. Why stop at 1 bit? Why not 8 bits or 12 bits or 16 bits? In fact, we only need 1) Trigger the sample and hold to hold the input value. one more insight and all of these possibilities snap into focus. We need to set 2) Guess that the digitized value is 1. Cấp giá trị logic 1 đó tới DAC 1 the most significant bit first. Let's work that out using a 2 bit converter. bit (1/2 dải đầy đủ của DAC, hay +2.5V). Again, use +5 volts full scale and have an input that we're trying to digitize of + 3 V. The values for a 2 bit DAC are -- oh, go ahead. Fill in the table: 3)Dùng một máy so mẫu theo dõi đầu ra DAC và giữ tín hiệu từ mạch lấy mẫu và giữ. Nếu giá trị được lấy mẫu ≥ 2.5 V thì đầu ra máy so DAC bits DAC Output V mẫu sẽ cao. Nếu< 2.5 V, đầu ra máy so mẫu sẽ thấp 00 4)Nếu đầu ra máy so mẫu cao, giá trị số hóa bằng 1; nếu không bit đơn 01 sẽ quá to để biểu diễn tín hiệu đầu vào, ra chuyển nó lại về 0 và kết 10 thúc. 11 Hình minh họa: Click to show table values. Mouse out to hide values. So now we can see how the ADC would arrive at the digitized value for output. 1) Set DAC to 10. DAC puts out 2.5 V 2) Comparator determines that sampled voltage is at least as great as the voltage produced by code 10. The 1 stays set. 3) Set the next DAC bit to 1, for a coding of 11. DAC outputs 3.75 V. 4) Comparator determines that the DAC output is greater than the sampled Lưu ý rằng, nếu đầu ra DAC lớn hơn đầu vào mạch lấy mẫu và giữ, voltage. The second bit gets turned off. đầu ra máy so mẫu sẽ cao và ngược lại. 5) Final encoding: 10. Tại sao lại dừng ở 1 bit àm khong phải 8, 12 hay 16 bit? trong thực tế, ta chỉ cần suy nghĩ một chút là sẽ tìm ra đáp án. Đầu tiên, chọn bit The digitization error in this case is 0.5 V; the resolution of the measurement quan trọng nhất bằng cách dung bộ chuyển đổi 2 bit. Lần nữa, dùng is only 1.25 V, so the closest representation of a 3 V input we can have is 2.5 thang +5V và đầu vào cần mã hóa +3V. Các giá trị cho DAC 2 bit như V. sau (điền vào bảng) Now let's make the leap to a 12 bit convertor. Resolution is now 1 part in 212. Bit DAC V đầu ra DAC Let's keep the conversion unipolar, full scale +5 V, and see how closely we 00 can digitize +3 V. 01 Fill in the second column in the table, check your work, then work out the third and fourth columns. "MSB" is the most significant bit (what would 10 correspond to the 1 bit example), while "LSB" is the 12th bit. In the third 11 column, you will have a 1 or a 0 for each bit. In the fourth column, sum the Giờ ta có thể thấy ADC đến các giá trị được số hóa cho đầu ra như thế values implied by the 1's and 0's in the second and third columns (Thus, if the nào? voltages for the 3 most significant bits were 2, 1, and 0.5 V and the binary values were 101, that would be 2*1 + 1*0 + 0.5*1 =2.5 V). 1) Đặt DAC tới 10. DAC sản ra 2.5 V Value for Cumulative 2) Máy so mẫu quyết định rằng hiệu điện thế lấy mẫu ít nhất cũng phải Bit Voltage +3V Approximate V lớn như hiệu điện thế tạo bởi mã 10 .The 1 stays set. MSB 3) Đặt bit DAC tiếp theo tới 1, để mã hóa 11. DAC đầu ra 3.75 V. 2 4) Máy so mẫu quyết định rằng DAC đầu ra lớn hơn hiệu điện thế 3 được lấy. Bit thứ 2 bị đóng. 4 5) Mã hóa cuối: 10. 5 Sai số số hóa trong trường hượp này là 0.5 V, đôh phân giải của phép 6 đo chỉ là1.25 V, vậy nên biểu diễn gần nhất của đầu ra 3V có thể có là 7 2.5 V. 8 Tiếp đến là chuyển đổi 12 bit. Giờ độ phân giải là 1/212. Giữ cho 9 chuyển đổi đơn cực, thang đầy đủ là +5V, xem kĩ +3V được số hóa thế 10 nào. 11 Điền vào cột 2 trong bảng, kiểm tra lại, và làm tính toán cột 3,4. LSB MSB= bit quan trọng nhất(tương đương với 1 bit), LSB= bit thứ 12. Trong côt 3 , sẽ có giá trị 1 và 0 cho mỗi bit. Trong cột thứ 4, tính tổng Click to show Voltage các giá trị cho bởi cột 2 và 3 của 1 và 0 (nếu hiệu điện thế cho 3 bit Double click to hide Voltage Click to show bit values quan trọng nhất là 2,1 và 0.5 V và các giá trị nhị phân là 101, thì sẽ là Double click to hide bit values Click to show cumulative V 2*1 + 1*0 + 0.5*1 =2.5 V). Double click to hide cumulative V Value Cumulative Bit Voltage There are several interesting things to see in the encoding. First, look at the for +3V Approximate V pattern of the digitized voltage: 100110011001. In hexadecimal, that's 999. MSB Why is there the repeating pattern? 3 V = 0.6 * 5 V in base 10. But 0.6*16 = 9.6, not an integer. 0.6 times ANY power of 2 (and thus for ANY grouping of 2 bits into nybbles, bytes, or words) does not give an integer, and thus 3 V 3 cannot be exactly represented in binary. Rather, it is represented as a 4 repeating "decimal" (heximal?) fraction. 5 Second, if you didn't carry enough significant figures with you along the way, you might have rounded off the final result with fewer non-zero bits. For 6 example, if you round off voltage values to 1.0 mV or finer, the coding is as 7 shown above. At 10 mV resolution, the 4 most significant bits, 1001, rounds 8 to 2.810 V. At 10011001, the summed voltage is 2.99 V. One could then get 3.00 V by setting the next bit, for a 10 bit approximation of 100110011. 9 Implicitly, this gives a 12 bit encoding of 100110011000. Inadequate 10 resolution (or noise) during digitization limits the precision of the final 11 encoding. LSB Hybrid Converters Có nhiều điều thú vị trong bảng mã này. Đầu tiên, nhìn vào mẫu hiệu Suppose there's a signal that is always between 2.8 and 3.2 volts. The first 4 điện thế được mã hóa: 100110011001.Trong hệ 16, nó là 999. Tại sao bits of the digitized word will always be 1001. Doesn't it seem wasteful (4 lại có dạng lặp lại này? 3 V = 0.6 * 5 V trong cơ số 10. Nhưng0.6*16 comparator operations!) to start fresh every time to convert these bits when it = 9.6, không phải số nguyên. 0.6 lần BẤT KÌ lũy thừa nào của 2 (vì is only the less significant bits that are changing? We could probably speed thế cũng như vậy với bất kì ghép nhóm của bit dưới dạng nybbles, up the conversion if we didn't waste time on digitizing the slowly-varying, bytes, hay words) cũng không cho số thực, vì vậy 3V không thể biểu large amplitude part of the potential. Engineers, being clever, have reached diễn dưới dạng nhị phân, mà biểu diễn dưới dạng phân số thập phân. the same conclusion and have designed hybrid ADCs that use flash Thứ hai, nếu không lấy đầy đủ chữ số có nghĩa trong quá trình, có thể converters for the most significant bits, then successive approximations (or mắc lỗi làm tròn xuống kết quả cuối cùng với ít bit khác không hơn. sigma-delta) for less significant bits. The first 8 bits are digitized in a single Ví dụ, nếu làm tròn xuống các giá trị hiệu điện thế tới 1.0 mV hay nhỏ cycle and feed the 8 most significant bits of the DAC. As long as the output hơn, mã sẽ như trên. Tại phân giải 10 mV , 4 bit quan trọng nhất, precision of the DAC is good enough, one can then do an analog subtraction 1001, làm tròn tới 2.810 V. Tại 10011001, hiệu điện thế tổng là 2.99 of the DAC output from the original (sampled) signal to provide the input for V. Có thể đạt được 3V bằng cách cài đặt bit tiếp theo, với gần đúng 10 the successive approximations part of the circuit. Here's a sketch: bit của 100110011. Nó cũng cho mã hóa 12 bit của 100110011000 Why digitize the 8 most-significant bits and then reconvert them to analog một cách hoàn hảo. Phân giải thiếu (hay nhiễu) trong quá trinh số hóa before subtracting? Recall that the comparators in the flash ADC are subject giới hạn độ chính xác của mã hóa cuối cùng. to error and thus they only approximately carry out digitization. If the output Chuyển đổi lai of the 8 bit DAC is PRECISE to 12-18 bits, then a precision offset can be Gỉa sử có một tín hiệu luôn ở giữa 2.8 và 3.2 V. 4 bit đầu tiên được mã introduced before the least-significant bits are digitized. The subtraction hóa sẽ luôn là 1001. Như vậy thật lãng phí cứ phải bắt đầu lại từ đầu amplifer (the bottom operational amplifier in the figure) can be designed with để chuyển đổi những bit này trong khi chỉ có những bit kém quan gain so that differences of a few millivolts between the sampled voltage and trọng hơn đang thay đổi. (tốn 4 máy so mẫu). Ta có thể tăng tốc quá the DAC output are presented to the second ADC at 2×, 10×, or 100× the trinh chuyển đổi nếu không lãng phí thời gian vào việc số hóa phần actual difference, so the second ADC can use higher, less noise-susceptible biên độ lớn và ít biến thiên của điện thế.Các kĩ sư đã rất thong minh potentials. Are there additional "gotcha"s? Yes -- and we'll discuss those tìm ra giải pháp và thiết kế ra các ADC lai- dùng chuyển đổi flash cho under Bits, Noise, and Linearity. các bit quan trọng, sau đó lấy xấp xỉ lien tiếp (hay sigma-delta) các bit kém quan trọng hơn. 8bit đầu được số hóa trong 1 chu trình duy nhất và cấp cho 8 bit quan trong nhất của DAC. Khi mà độ chính xác đầu ra của DAC còn đủ tốt, có thể tiến hành trừ analog đầu ra của DAC khỏi tín hiệu gốc( tín hiệu được lấy mẫu) để cho ra các xấp xỉ lien tiếp ở các đầu vào. Đây là sơ đồ:

Tại sao số hóa 8 bit quan trọng nhất và sau đó chuyển chúng sang analog trước khi trừ? Nhớ rằng, các máy so mẫu trong ADC flash chắc chắn là có sai số và vì thế chúng chỉ có thể tiến hành số hóa một cách tương đối.Nếu đầu ra của DAC 8 bit chính xác tới 12-18 bit, thì phần bù chính xác có thể được đưa vào trước khi những bit ít quan trọng nhất được số hóa. Khuyếch đại trừ (ở đáy của hình vẽ) có thể được thiết kế với bộ tăng để sự khác biệt của vài mV giữa hiệu điện thế được lấy mẫu và đầu ra của DAC biểu diễn được tới đơn vị giây ở các cấp độ gấp 2, 10, 100 lần sự khác biệt thực sự, vì thế ADC thứ 2 có thể dùng các điện thế cao hơn, ít nhiễu hơn. Có gì thắc mắc sẽ thảo luận tiếp trong Bits, Noise, and Linearity.

Dual Slope ADC Choose Subtopic Successive Sample and Hold Comparators Flash ADC Approximations Settling Time ADC Voltage to Bits, Noise, and Dual Slope ADC Sigma-Delta ADC Frequency ADC Linearity For the ADCs discussed to this point, a time-varying signal was sampled or the ADC operated so rapidly that, for practical purposes, the signal did not change during a single conversion. Now we go to the other time extreme. What if there is a noisy signal, and we desire to digitize its average value? For example, what if we're looking at a flickering candle and we want to know the average illumination? One strategy would be to digitize at a high rate (say, with a successive approximations ADC) and average the results. But another strategy is to do signal averaging in the midst of the digitization process, thus simplifying the electronics. The dual slope ADC is one of several devices that work in this way. How long does it take to go down a flight of stairs? "It depends how many ADC đường dốc kép steps there are," you obviously reply. The idea behind a dual slope ADC is to Với các ADC đã được thảo luận cho tời thời điểm này, một tín hiêu have the unknown signal set the height of the stairs, and then to use a quiet, biến đổi theo thời gian hay ADC hoạt động rất nhanh đến mức, trong well-controlled reference to descend the stairs at a known rate. If we know các mục đích sự dụng thiết thực, các tín hiệu không thay đổi trong một the rate, and we measure the time, we know how high the stairs are. Now let's lần chuyển đổi. translate that into electronics. Nếu có tín hiệu nhiễu thì sao? làm sao để mã hóa gí trị trung bình của Aside from comparators, the most important analog part of a dual slope ADC nó. Ví dụ, nều nhìn vào ngọn nến đang cháy và muốn biết độ sang is an integrator. The circuit is: trung bình của nó. Một cách là mã hóa ở tốc độ cao (với ADC lấy xấp xỉ lien tiếp) và lấy trung bình các kết quả. Nhưng một cách khác là lấy trung bình các tín hiệu ngay trong quá trình mã hóa, do đó đơn giản Vout is the integral of Vin, or actually hóa về mặt điện tử. ADC đường dốc kép là một trong các thiết bị làm việc theo cách này. Any time one wants to reset the integral to 0, one simply shorts the capacitor. Mất bao lâu để đi xuống một dãy các bậc thang? Chắc chắn bạn sẽ nói: Notice the negative sign -- positive input voltages give negative output “Nó phụ thuộc vào việc có bao nhiêu bước”. Ý tưởng đằng sau ADC voltages. đường dốc kép là cho các tín hiệu không biết tạo nên độ cao của cầu If we want to digitize a postive voltage, we'll also need a reference voltage thang, và dùng một hệ qui chiếu tĩnh, dễ kiểm soát để đi xuống cầu that's negative (and, of course, if we want to digitize negative voltages, we thang theo một vận tốc đã biết. Nếu ta biết vận tốc, và tiến hành đo need a positive reference). We integrate the unknown voltage Vin(t) for a fixed thời gian, ta sẽ biết được độ cao của cầu thang. Giờ hãy dịch ý tưởng time T. For now, let's assume the potential is constant in time. The integral này sang ngôn ngữ điện tử. will be -VinT/RC. Now disconnect the input potential. Since the input is 0, the Ngoài các máy so mẫu, phần analog quan trọng nhất của ADC đường integral holds constant. Next, connect the input to the reference voltage dốc kép là một mạch tích phân. Mạch đó như sau (opposite sign to Vin) and integrate. What will happen? The integrator will ramp towards 0. How will we know when we get to zero? Multiple choice, choose the right component: Operational Amplifier Digital to Analog Converter Comparator

How long will it take for the integrator to reach zero? Long enough to exactly give the same magnitude but opposite sign integral we just computed above. Leaving out the signs, VinT/RC = VrefTdown/RC. How convenient -- the RC Vra là tích phân của Vvào, hay thực sự là values cancel. Tdown=VinT/Vref. Since T and Vref are fixed, the time that the down count takes is proportional to the input voltage. If we're clever (and why wouldn't we be?), we can get the down-count time to read out as if the units were volts. If the magnitude of Vref is 5 V, and the input voltage that we're trying to measure is 1.000 V, then we want something that will count to 1000 time units. Suppose we have a clock that puts out one pulse every 10 μs. Bất cứ khi nào muốn đặt lại tích phân về 0, chỉ cần làm đoản mạch tụ Then if Tdown is 1000 × 10 μs, we have it. But that makes Tdown=10 ms, so T điện. Chú ý là hiệu điện thế dương đầu vào cho hiệu điện thế âm ở đầu (the integration time) must be set to 10 ms * 5.000 V/1.000 V = 50 ms. But ra. once we set the initial integration time to 50 ms, the time that it takes to return to 0 will read out in voltage directly. For example, if we integrate Nếu muốn số hóa một hiệu điện thế dương, ta cũng cần một hiệu điện 2.345 V for that same 50 ms, then the discharge back to zero will take 2345 thế qui chiếu là âm (và ngược lại). Ta lấy tích phân của hiệu điện thế ticks of the 10 μs clock, and we have the readout as we wanted it. Here's a không biết Vin(t) trong thời gian T cho trước. Giờ giả sử điện thế sketch of what we just said: không đổi theo thời gian. Tích phân sẽ là -VinT/RC. Giờ cắt điện thế đầu vào. Vì đầu vào bằng 0, tích phân sẽ là hằng số. Tiếp theo,nối đầu vào với hiệu điện thế qui chiếu(ngước dấu vớiVin và lấy tích phân. Điều So why do it this way? Suppose that there is noise on top of the input voltage. gì sẽ xảy ra? Mạch tích phân sẽ là đường gồ ghề tiến về 0. Làm sao By integrating, we average out the noise, thus getting a precise measurement biết được khi nào chúng tới 0. Lựa chọn bộ phận đúng: of the input potential. Additionally, measuring time precisely is easier than Khuyếch đại Chuyển đổi số-analog Máy so mẫu measuring potential precisely. We can get additional bits in our measurement by using a faster clock (and thus a higher count for the same discharge time) Phải mất bao lâu thì mạch tích phân tới đượ 0? Đủ lâu để đạt được much more easily than by adding bits to a flash or successive approximation chính xác độ lớn nhưng ngược dấu với tích phân ta vừa dựng được ở converter. For the same mean as in the sketch above, a noisy signal would be trên. Bỏ qua dấu VinT/RC = VrefTdown/RC. Bỏ giá trị RC, ta có: digitized thus: Tdown=VinT/Vref. Do T và Vref là cố định, thời gian đếm ngược tỷ lện với hiệu điện thế đầu vào.Nếu nhanh trí, ta có thể lấy thời gian đếm ngược để đọc ra Volt. Nếu độ lớn của Vref là 5 V, và hiệu điện thế đầu vào The zig-zag increase in potential is due to noise on the input signal, but that đang cố đo là 1000 V, ta muốn đếm 1000 đơn vị thời gian. Gỉa sử có averages out over time T. chiếc đồng hồ tạo xung 10 μs /lần, nếu Tdown là 1000 × 10 μs, ta hoàn Remember that there are multiple ways to format binary numbers? Which of toàn có thể tạo ra một chiếc đồng hồ như vậy. Nhưng nếuTdown=10 ms, the common forms would be easiest to use with a dual slope ADC? thì T (thời giân lấy tích phân) phải được chỉnh về 10 ms * 5.000 V/1.000 V = 50 ms. Nhưng khi ta đặt thời gian lấy tích phân ban đầu Signed Magnitude Twos Complement Straight Binary tới 50 ms, thì thời gian để trở về 0 sẽ được đọc trực tiếp từ hiệu điện thế. Ví dụ, nếu lấy tích phân 2.345 V trong 50 ms, thì sự phóng điện trở lại 0 sẽ mất 2345 tích tắc của 10 μs , và ta có chỉ số đọc như mong Let's put the pieces together. What would a complete dual slope ADC look muôn. Đây là sơ đồ của những điều vừa được nói: like inside? We'll leave out the details of the counter/controller. Dashed lines mean "control" (to throw a switch or convey a pulse). Solid lines carry analog potentials. The circuit is:

Click for larger view. The system works in 3 stages: 1) short the capacitor to set the integrator to 0.

2) integrate Vin for fixed time.

3) use either Vref or - Vref to drive the integrator back to zero, with the timer measuring the elapsed period until a "stop" pulse is received from the comparator observing the output of the integrator. The time than transfer Tdown to the display, where it is shown until the completion of the next 3 step cycle. Tại sao ta phải kàm theo cách này? Giả sử có nhiễu trên đỉnh của hiệu In the days when analog integrated circuits were cheaper and more familiar to điện thế đầu vào, bằng cách lấy tích phân, ta làm trung bình hóa độ designers than digital circuits, the dual slope ADC was the choice for nhiễu, và vì thế đo được chính xác điện thế đầu vào.Hơn nữa, đo thời inexpensive multimeters, anything that didn't require high speed, and gian một cách chính xác còn dễ hơn đo điện thế một cách chính xác.Ta especially any problem that looked at noisy signals. Now that có thể tạo thêm bit trong thiết bị bằng cách cộng bit với một máy microcontrollers with high speed ADCs and facile signal averaging are chuyển đổi flash hay chuyển đổi xấp xỉ liên tiếp. Tương tự như trong available, the dual slope system is becoming less common. Nevertheless, hình vẽ trên, tín hiệu nhiễu cũng được số hóa, vì thế when considering measurement of noisy signals, as long as conversion rates of no more than 10 times per second are adequate, this is an approach that is well worth considering. The sigma delta ADC, linked with a digital signal processor or microcontroller, is becoming the chief challenger to the dual slope system. Next

Đường tăng hình zig-zag về điện thế là do nhiễu trên tín hiệu vào,nhưng nó được trung bình hóa theo thời gian. Nhớ rằng có nhiều cách tạo số nhị phân? Cách nào trong số các cách thông thường là dễ dùng nhất với ADC đường dốc kép. Signed Magnitude Twos Complement Straight Binary Sắp xếp lại các dữ kiện đề bài cho, vậy bên trong mạch ADC đường dốc kép sẽ như thế nào? Bỏ qua các ci tiết máy đếm, máy kiểm tra. Đường nét đứt nghĩa là "kiểm soát" (để chuyển đổi công tắc hoặc truyền 1 xung).Đường nét liền mang các hiệu điện thế analog. MACH ĐIỆN:

Ấn xem hình to hơn. Hệ thống làm việc trong 3 giai đoạn: 1) làm đoản mạch điện dung , chuyển mạch tích phân về 0.

2) lấy tích phân Vin .

3) Dùng Vref hay - Vref để kéo mạch tích phân chuyển về 0, đo thời gian trôi qua cho đến khi nhận được một xung “ dừng lại từ máy so mẫu đang giám sát đầu ra của mạch tích phân Sau đó Tdown được chuyển đến bộ phận hiển thị và nó tiếp tục ở đó cho đến khi hoàn thành chu kì 3 bước tiếp theo.số, ADC đường dốc kép là lựa chọn của Trong thời kì mạch tích phân analog rẻ hơn và phổ biến hơn mạch số, ADC đường dốc kép là lựa chọn lí tưởng cho các vạn năng kế rẻ tiền- không cần tốc độ nhanh, không nhiễu. Giờ đây với các thiết bị kiểm soát vi mô có ADC tốc độ cao và có khả năng trung bình hóa tín hiệu dễ dàng, hệ thống đương dốc kếp trở nên kém thong dụng. Tuy nhiên, khi nói đến phép đo các tín hiệu nhiễu, trong phạm vi tốc độ chuyển đổi không lớn hơn 10 lần/giây thì đây vẫn là một phương pháp đáng coi trọng. Sigma delta ADC, được kết nối với thiết bị xử lí tín hiệu số hoặc điều khiển vi mô, đã trở thành kẻ thách thức chính tới hệ ADC đường dốc kép.

Voltage to Frequency Conversion ADC Choose Subtopic Successive Sample and Hold Comparators Flash ADC Approximations Settling Time ADC Voltage to Bits, Noise, and Dual Slope ADC Sigma-Delta ADC Frequency ADC Linearity Since an analog to digital converter ends up producing a number, wouldn't it be convenient if we could simply count something and have that something proportional to the potential being measured? A voltage to frequency converter ADC does just that. A voltage is integrated until it reaches some pre-set threshold, at which point a comparator trips, doing 2 things: 1) short circuit the capacitor, resetting the integrator to zero. 2) produce a pulse that is counted. Here' the circuit.

V to F converters integrate noise, and so are useful under circumstances ADC chuyển đổi hiệu điện thế sang tần số similar to dual slope units. V to F ADCs are precise, accurate, simple, and Vì bộ chuyển đổi analog sang số tạo ra một số, nên sẽ không thuận inexpensive. The precision is directly proportional to the time over which tiện nếu ta chỉ có thể tính một thứ gì đó và có một thứ gì đó chỉ tỉ lệ counting occurs, and inversely proportional to the time required to integrate a với điện thế được đo. Một chuyển đổi ADC từ hiệu điện thế sang tần single count. số giải quyết được vấn đề đó. If we count pulses for a fixed period of time, then we know how often the Một hiệu điện thế được tích phân cho đến khi nó đạt được một ngưỡng comparator tripped during that time. Suppose we want to display 1.000 for a định trước nào đó, tại đó nếu máy so mẫu bị chặn/ vướng thì làm 2 1 V input, and suppose we look at the input for 1.000 s. Then we'd want the bước như sau: comparator to trip 1000 times per second. Further, suppose the comparator is set up to trip at a potential of 5 V (chosen just so it's not the same as the input potential; in fact, this potential can be anything we like as long as we know it 1) làm đoản mạch tụ điện, cài đặt lại mạch tích phân về 0 in advance). Then a 1 V input should integrate to 5 V in 1 ms. In the dual 2) tạo xung đếm. slope module, we explained how integrators work. From the argument there, Đây là sơ đồ mạch. the RC time constant of the integrator is set by Vout = - VinT/(RC). Ignoring sign, 5 V = 1 V * 1 ms/RC. RC = 1 ms/5 = 200 μs. For R = 1 kΩ, C = 0.2 μF. Changing the expected magnitude of the input voltage or the number of significant figures desired may mean a different integration time, R, or C value, but for a wide range of inputs the integrate, short, count, repeat cycle works well. The first very high resolution (up to 6 digits or ~ 20 bits) ADCs worked on this principle. The non-idealities of a V to F converter are dependent on the design strategy. Let's start the simplest approach. Here, we do nothing to compensate for the time required to fully discharge the capacitor; the time while the capacitor is discharging called "dead time." The bigger the resistance of the switch used to short the capacitor, the longer the switch must be closed. Alternatively, if Chuyển đổi từ V sang F trung bình hóa nhiễu, và vì thế hiệu quả trong the switch isn't closed for long enough, there will be residual potential on the các trường hợp tương tự với các thiết bị đường dốc kép. V- F ADCs integrator, and the time to integrate to threshold will be reduced. In practice, chính xác, ít lệch, đơn giản, rẻ tiền. Độ chính xác tỉ lệ thuân với thời if one knows how long the switch is closed, one knows how long the dead gian đếm, và tỉ lệ nghịch với thời gian cần thiết để hợp nhất một lần time is, and a correction factor may be computed. đếm. Example. Suppose the integrator in a V to F converter is shorted for 1 μs Nếu đếm xung trong một khoảng thời gian xác định, sẽ biết được tần every time the comparator "hits." In 1.0000 s, the V to F counts up 9997 suất các máy so mẫu thường bị vướng trong thời gian đó. Giả sử muốn counts, seemingly indicating 0.9997 V. However, that means that the biểu diễn 1000 cho 1V đầu vào, và giả sử cho đầu vào 1000s. Nhiệm integrator wasn't integrating for 9997 μs or 9.997 ms. Because the apparent vụ của máy so mẫu là trượt 1000 lần/s. Hơn nữa, giả sử máy được cài count rate was 1 count every 1/9997 s or once per 0.1 ms, the counter missed đặt để có thể trượt ở điện thế 5V( chọn sao cho khác với điện thế đầu integrating for nearly 100 counts. The corrected count is 9997 + 100 = 10097, vào, thực tế, điện thế này có thể có giá trị bất kì chừng nào mà ta hiểu giving a corrected output reading of 1.0097 V, about a 1% correction. về chúng để chọn). Sau đó, 1V đầu sẽ tích phân thành 5V/1ms. While correction factors are easier to account for in software than in Trong phần đường dốc kép, Ta đã lý giải mạch tích phân làm việc thế hardware, many systems account for the dead time in hardware. nào. Từ lí luận trên, hằng số RC của mạch tích phân được cài đặt Is there a way to get rid of the dead time? Yes. We can integrate in one bởiVra = - VvàoT/(RC). Bở qua dấu 5 V = 1 V * 1 ms/RC. direction until we reach one threshold level, then integrate in the opposite RC = 1 ms/5 = 200 μs.Với R = 1 kΩ, C = 0.2 μF. Thay đổi độ lớn sense until a second threshold (possibly zero, though usually a bit above zero mong muốn của hiệu điện thế vào hay số chữ số có nghĩa mong muốn to avoid noise in the zero level) is reached. We continue switching back and có thể tương đương với một thời gian lấy tích phân, giá trị R, C khác, forth, with the error due to switching time typically small compared to dead nhưng đối với phạm vi lớn các đầu vào, thì tích phân, đoản mạch, lặp time error. We get one count for each combined up/down cycle. One might chu kif đều thực hiện tốt. Gía trị độ phân giải cao (tới tận 6 chữ số hay think that needing two comparators would be expensive and complex. ~ 20 bit) cũng đúng khi áp sụng phương pháp này. Fortunately, early in the era of integrated circuits, the 555 timer was Sự không lý tưởng của chuyển đổi V-F phụ thuộc vào cách thiết kế. fabricated. It goes "High" when an input voltage is 2/3 of a reference, then Tiếp cận vấn đề một cách đơn giản, ở đây, ta không phải bù cho switches "Low" when the input to a second input drops to 1/3 of the same khoảng thời gian cần thiết để nạp điện đầy tụ điện; thời gian trong lúc reference. The reference can be the power supply potential (cheap, simple, tụ phóng điện gọi là “thời gian chết”. Nếu công tắc đoản mạch tụ điện readily available) or a separate, carefully controlled reference (more precise). có điện trở cang lớn, thì càng cần để công tắc đóng trong thời gian dài. Here's the circuit: Nói cách khác, nếu công tắc không được đóng trong thời gian đủ dài, sẽ vẫn còn điện thế lưu trên mạch tích phân, và thời gian đểtichs phân tới ngưỡng càng bị giảm. Trong thực tế, nếu biết công tắc đóng bao A 555 timer can toggle reliably at at least 100 kHz, so 1 s integrations can lâu , thì cũng biết khoangr thời gian chết là bao lâu, và có thể tính have 5 significant figures. 10 s integrations? 6 significant figures, provided được hệ số điều chỉnh. only that there's no drift in the values of R, C, Vref, or the mean of Vin during this time. Ví dụ. Giả sử mạch tích phân trong moth chuyển đổi V-F bị đoản mach trong 1 μs mỗi lân máy so mẫu đánh vào. Trong 10000s, bộ đếm Next V-F đếm được 9997 lần, cho biết 0.9997V. Tuy nhiên, mạch tích phân không lấy tích phân cho 9997 μs hay 9.997 ms. Vì tốc độ đếm là 1/9997 s hay 1/ 0.1 ms, máy đếm đã bỏ qua tích phân cho gần 100 lần đếm. Số lần đếm đúng là 9997 + 100 = 10097, nên số đọc được hiệu chỉnh là 1.0097 V, hiệu chỉnh cỡ 1%. Trong khi hệ số hiệu chỉnh dễ chiếm % nhiều hơn do phần mềm hơn là phần cứng, nhiều thiết bị lí giải % nhiều là do thời gian chết ở phần cứng. Vậy có cách nào loại được thời gian chết? Có, ca có thể tích phân theo 1 hướng cho đến khi chạm ngưỡng của một mức, sau đó tích phân theo hướng ngược lại cho đến khi chạm ngưỡng khác( có thể là 0, thường là trên 0 một chút để tránh nhiễu trong mức 0). Ta tiếp tục chuyển xuôi và ngược, lỗi do thời gan chuyển khá nhỏ so với lỗi do thời gian chết. Ta được tính một lân cho mỗi chu ki kết hợp trên/ dưới. Có thể cho rằng việc cần 2 máy so mẫu là đắt đỏ và phức tạp. Nhưng may thay, trong thời kì đầu của mạch tích phân, thiết bị bấm giờ 555 đã được chế tạo. Nó tăng khi có hiều điện thế bằng 2/3 hiệu điện thế gốc. Gốc có thể là điện thế cung cấp năng lương( rẻ, đơn giản, có sẵn) hay gốc riêng rẽ, được kiểm soát (chính xác hơn). Đây là mạch:

Một thiết bị bấm giờ 555 timer vận hàn một cách tin cậy ở ít nhất 100 kHz, nên 1 s tích phân có thể có 5 số có nghĩa. 10 s tích phân? 6 số có nghĩa, miễn sao không có độ lệch của R,C,Vref, hay trung bình của Vin trong thời gian này.

Sigma-Delta ADC Choose Subtopic Successive Sample and Hold Comparators Flash ADC Approximations Settling Time ADC Voltage to Bits, Noise, and Dual Slope ADC Sigma-Delta ADC Frequency ADC Linearity We now come to a type of ADC that has become the tool of choice for audio digitization for computers, for inexpensive high-resolution digitizers, and for digital signal processors that need not digitize at high speeds: the sigma-delta (or, if the font display allows it, the Σ-Δ converter). Because the response frequency and signal averaging properties are as good as dual slope and V to F converters, the resolution better than many successive approximation converters and as good as many V to F systems, but the hardware is simpler to build and less subject to drift, in recent years the Σ-Δ converter has ADC Sigma-Delta exploded in popularity. The only ADC whose hegemony is not threatened by the Σ-Δ converter is the flash converter. Dạng ADC này đã trở thanh công cụ số hóa âm thanh cho máy tính, thiết bị số hóa phân giải cao giá thành thấp, và cho máy xử lí tín hiệu Exercise: what is unique about flash converters that makes it unlikely that số không cần tốc độ số hóa cao(hoặc nếu font biểu diễn cho phép, sẽ they will cease being used? đóng cả vai trò chuyển đổi Σ-Δ). Bởi đặc tính của tần số đáp ứng và Click to display answer. trung bình tín hiệu cũng tốt như chuyển đổi đường dốc képvà V to F, phân giải tốt hơn nhiều chuyển đổi xấp xỉ liên tiếp khác và tôt ngang A Σ-Δ converter runs perpetually, seeking to produce an analog output that hệ V to F, nhưng phần cứng thì đơn giản và ít lệch, trong những năm matches the input potential. It does this by integrating the difference between gần đây, chuyển đổi Σ-Δ đã trở nên rất thông dụng. ADC duy nhất the output of a 1 bit DAC and the value of the input signal. The DAC outputs không bị mất đi sự phổ biến là chuyển đôi flash. either +Vref or -Vref. If the input potential is 0, then, on average, half the time the DAC will need be set to logical 1 (+Vref), and half the time to logical 0 (- Bài tập: Chuyển đổi flash có gì đặc biệt mà ta không thể ngừng sử Vref). A comparator looks at the difference between the integrated voltage on dụng nó? Ấn xem trả lời the capacitor and the instantaneous input. While positive noise bursts may Một chuyển đổi Σ-Δ chạy liên tục, tìm đầu ra analog phù hợp với hiệu lead to a burst of counted pulses, negative noise bursts will lead to a period điện thế đầu vào. Nó thực hiện quá trình này bằng cách tích phân sự during which pulses are absent. By continously chasing perfection, the counts khác biệt giữa đầu racủa DAC 1 bit và giá trị của tín hiệu đầu vào.Đầu from noise average out. One counts the number of logical 1's over a fixed ra DAC có thể là +Vref hay -Vref. Nếu hiệu điện thế vào là 0, thì tính period, knowing that all 1's implies an input of +Vref or greater, all 0's implies trung bình, trong suốt nửa quá trình làm việc, DAC cần được đặt -Vref or less, and all counts in between imply intermediate values. The logical 1 (+Vref), và nửa thời gian logical 0 (-Vref). Một máy so mẫu comparator/integrator/1 bit value setting has to occur many times for each giám sát sự khác biệt giưa hiệu điện thế trên tụ điện và đầu ra tức thời. digitization. In fact, typically, one oversamples, that is, measures the signal Trong khi một loạt nhiễu dương có thể dẫn tới một loạt xung được more than the minimum plausible number of times before outputting a single đếm, một loạt nhiễu âm sẽ dẫn tới một thời gian vắng mặt của xung. value. Suppose one seeks an output precise to 24 bits. That's about 1 part in Bằng cách tìm liên tục sự thống nhất, các lần đếm nhiễm dần bị trung 16 million. At an oversampling of 16, that means 16*16 milliion = 256 million comparisons must have been made. For a single integrator/single bit bình hóa. Tính số logical 1 trong một khoảng thời gian xác định,biết DAC, that would allow 1 conversion per second with this oversampling and a rằng tất cả1's liên quan đến đầu vào +Vref hoặc lơn hơn, tất cả 0 liên comparison made every 4 ns. In practice, one doesn't simply count pulses quan đến -Vref hoặc nhỏ hơn, và các lần đếm giữa chúng liên quan tới flat-footedly, but rather digitally filters the bitstream. The result is that a giá trị trung bình. Máy so mẫu/máy tích phân/cài đặt giá trị 1 bit xảy nominal 24 bit ADC can be speeded up to be a multi-kilohertz, lower ra lặp lại trong mỗi lần số hóa. Thực tế, thông thường là một mẫu lấy resolution device, or slowed down to be a full 24 bit, few-Hertz-converter. quá, tức là đo tín hiệu nhiều hơn số lần cực tiểu có thể trước khi cho There are at least three good web sources for explanation of what is going on. đầu ra một giá trị. Gỉa sử, nếu cần đầu ra chính xác tới 24 bit, cỡ 1/16 First see the Σ-Δ simulator at the Analog Devices website. Second, look at triệu. Tại 1 mẫu lấy quá 16, tức là đã làm tất cả 16*16 triệu = 256 triệu Maxim's Application Note 1870 (you'll find the parent website has a wealth so sánh.Với mạch tích phân đơn/DAC đơn bit, cho phép1 chuyển đổi/s of information on ADCs of all varieties). Third, Bonnie Baker, in a series of với mẫu lấy quá và tiến hành so sanh mỗi 4 ns. Trong thực tế, không columns in EDN in 2007-2008 gave a thorough analysis of how Σ-Δ chỉ đơn giản là đếm xung, mà còn phải lọc số trong dòng các bit. Kết converters work. See Part 1, Part 2, Part 3, and Part 4 (and, incidentally, look quả là DAC định danh 24 bit có thể được tăng tốc tới nhiều KHz, làm around the EDN website for other useful commentary on ADC use). giảm độ phân giải hay chậm tới 24 bit, ngang với chuyển đổi cỡ vài MHz . Có ít nhất 3 nguồn giải thích khá rõ . Bước1, xem mô hình Σ-Δ ở web về thiết bị analog. Sau đó đọc Maxim's Application Note 1870 (sẽ thấy the parent website có thông tin về các loại ADC). thứ 3, Bonnie Baker, trong chuỗi bài báo EDN in 2007-2008 phân tích Σ-Δ chuyển đổi thế nào. Xem Part 1, Part 2, Part 3, và Part 4 (xem luôn EDN website để tìm các chỉ dẫn về sử dụng ADC)

Bits, Noise, and Linearity; the Imperfections of ADCs Choose Subtopic

Successive Sample and Hold Comparators Flash ADC Approximations Settling Time ADC Voltage to Bits, Noise, and Dual Slope ADC Sigma-Delta ADC Frequency ADC Linearity

Now that we've seen how a variety of ADCs work, how can we compare and contrast their behavior? Comparisons can be drawn in many ways: Number of useful bits and encoding scheme Digitization rate (frequency) Bandwidth (not necessarily the same as digitization rate) Linearity, missed codes Signal-to-noise ratio Full scale range Differential vs. single-ended Bits, Nhiễu, và độ tuyến tính; các khuyết điểm của ADCs Communications interface Biết cách làm việc của ADC, so sánh và phân biệt các đặc điểm của chúng? So sánh theo nhiều cách: Number of useful bits and encoding scheme số bit có ích và cách mã hóa Just because an ADC is physically wired for some number of bits does not necessarily mean that all those bits will be valid under all circumstances. tốc độ số hóa (frequency) Suppose we think of a 16 bit successive approximations ADC. 3/4 of the way độ rộng của dải (not necessarily the same as digitization rate) through doing a conversion, the 12 most significant bits have been set. If we độ tuyến tính, mã thiếu simply read out those bits, we have used a 16 bit device to do a 12 bit conversion. Any successive approximations or Σ-Δ scheme be modified so tỉ số tín hiệu-nhiễu that one can sacrifice resolution in order to gain speed (or vice versa). thang đo đầy đủ Similarly, a V to F converter may have hardware allowing, say, 20 bits resolution for a 1 V full scale measurement lasting 10 s. That same hardware vi sai - một đầu would measure 17 bits in 1.25 s (1/8 time = (1/2)3, so 3 fewer bits). giao diện truyền thông Exercise: For the V to F system described above, how long would it take to Số lượng bit có ích cách mã hóa do an 8 bit conversion? ADC có dây ở một vài bit không có nghĩa tất cả các bit này đều dùng Click for answer được trong mọi trường hợp Ví dụ ADCxấp xỉ liên tiếp16 bit . and explanation Trong3/4 quá trình chuyển đổi, 12 bit quan trọng nhất được cài đặt. Given the answer to the first part of this exercise, if you only wanted 8 bits Nếu chỉ đọc những bit này, ta đã dùng thiết bị 16 bit để làm một resolution, would you choose this V to F system or a flash converter? chuyển đổi 12 bit.Bất cứ cách mã hóa xấp xỉ liên tiếp nào hay mã hóa Click for answer Σ-Δ biến đổi để giảm bớt độ phân giiar và tăng tốc độ (hoặc ngược lại) and explanation Tương tự một chuyển đổi V- F có thể có phần cứng cho phép thực hiện được, 20 bits phân giải cho phép đo toàn thang 1 V kéo dài 10 s. The coding scheme matters as well. A 12 bit converter, operating in 2's Phần cứng tương đưng cũng đo được 17 bits trong 1.25 s (1/8 thời complement binary mode, generates 11 bits of magnitude information, plus a gian = (1/2)3, nên ít hơn 3 bits). sign bit. But what if we know the sign of the data in advance? Then coding in straight binary gives the potential for twice the resolution in the Bài tập: Với hệ V-F mất bao lâu để chuyển dổi 8 bit? Nếu chỉ muốn measurement. If the ADC codes as offset binary but the computer to which it phân giải 8 bit, dung hệ V-F hay chuyển đổi flash? is interfaced uses 2's complement binary, software to convert each incoming Cách mã hóa cũng là một vấn đè. 1 chuyển đổi 12 bit , hoạt động trong piece of data is required, slowing down data reduction. If an ADC is to trạng thái bù nhị phân của 1, cho 11 bit về thông tin độ lớn, 1 bit về directly drive a digital display, one must know if the display controller dấu. Nhưng nếu đã biết dấu trước thì sao? expects straight binary (plus sign), offset binary, or 2's complement binary Mã hóa trong hệ nhị phân chuẩn sẽ cho độ phân giải gấp 2 trong coding, or the display will be in error even if the ADC is working correctly. phéop đo. Nếu ADC mã hóa như phần bù nhị phân nhưng máy tính nó Finally, some displays expect decimal input. While we did not discuss ADCs chuyển tiếp tới lại dùng hệ nhị phân bbuf của 2 thì cần phải có phần that directly digitize in decimal, they do exist (wasting coding space -- the mềm để chuyển đổi các mảnh dữ liệu đầu vào, giảm mất dữ liệu. Nếu highest resolution for transistor or lead possible is with binary coding). ADC nối trực tiếp tới phần hiển thị số, phải biết được trình điều khiển Digitization rate (frequency) hiển thị muốn ở dạng chuẩn(có dấu), bù, bù của 2 hay trình sẽ báo lôi ngay kể cả khi ADC hoạt động tốt.Cuối cùng, phần hiển thị muốn đầu How rapidly does the ADC refresh its output? That's the digitization rate. ra thập phân không?. Trong khi ta không thảo luận ADC số hóa trực Approximate rates are tabulated below (but one must look at the tiếp trong hệ thập phân, thì chúng vẫn có tồn tại( nhưng tốn chỗ cho specifications for each system; just knowing the type isn't enough!). mã hóa—độ phân giải cao nhất của transitor hay bộ chỉ huy chỉ có thể Digitization Rate thực hiện được bằng mã hóa nhị phân). ADC Type Number of bits (Hz) Tốc độ số hóa (tần số) Dual Slope 12-18 1-100 Tốc độ số hóa là tốc độ ADC làm mới đầu vào của nó . Tốc độ tương đối trong bảng sau (tùy thuộc mỗi hệ riêng) V to F 12-24 1-1000 Loại ADC Số bits Tốc độ số hóa (Hz) Successive Đường dôc kép 12-18 1-100 12 105 - 20×106 Approximations V - F 12-24 1-1000 Xấp xỉ liên tiếp 12 105 - 20×106 16 104 - 4×106 16 104 - 4×106 Flash 8 106 - 108 Flash 8 106 - 108 Σ Δ 14-24 1-1.92×105 Σ Δ 14-24 1-1.92×105 Nói chungm phân giả cao thì chuyển đổi chậm . Một vài loại phức tạp In general, higher resolution correlates with slower conversion. Some ( chuyển đổi pipelined) pha trộn giữa chuyển đổi flash cho các bit compound types (pipelined converters) may mix a flash converter for the quant rọng nhát với một vài kiểu khác cho các bit ít quan trọng hơn. most significant bits with some other strategy for less significant bits. Độ rộng dải (không cần phải giống tốc độ số hóa) Bandwidth (not necessarily the same as digitization rate) Tần số Nyquist cho hệ ADC là gì? Nó phụ thuộc mạch analog trước khi chuyển đổi.Nếu mạc có hằng số thời gian RC dài hơn thời gian What is the Nyquist frequency for the ADC system? That depends on the giữa các chuyển đổi, thì mạch tạo thành dải hiệu quả của ADC. Tần số analog circuitry preceding the converter. If the analog circuitry has an RC analog cao hơn bị chặn và giảm hiệ tượng giả danh. Mặt khác, nếu hệ time constant longer than the time between conversions, then that circuitry thống analog nhanh, tần số Nyquist trở thành 1/2 của tần số lấy mẫu. sets the effective bandwidth of the ADC. Higher analog frequencies are Vì thế, 1 mẫu lấy xấp xỉ liên tiếp ADC ở 1 MHz có tần số Nyquist là suppressed, reducing the likelihood of aliasing. On the other hand, if the 500 kHz trừ khi có 1 analog đầu cuối giảm tần số đến dưới mức giá trị analog system is fast, the Nyquist frequency becomes 1/2 the sampling này. Với nhiều hệ phức tạp, nêys vả đầu cuối và mẫu lấy đều qua trọng frequency. Thus, a successive approximations ADC sampling at 1 MHz has a thì tần số Nyquist là tổng căn bậc 2 của các thành phần; phần chậm Nyquist frequency of 500 kHz unless a slower analog front end reduces the 2 -2 - nhất chiếm giá trị nhiều nhất. Vì thế Δν Nyquist,total=(Δν Nyquist,Analog + Δν frequency to below this value. As with many compound systems, if both front 2 -2 Nyquist,Digital) . Chú ý tần số analog Nyquist ở trên tần số số end and sampling are important, the overall Nyquist frequency is a root- Nyquist,hiện tượng gả danh sẽ xuất hiện và cần phân tích dữ liệu để mean-square combination of the components. One must be a bit careful; the 2 -2 - kết luận về hiện tương này. SLOWEST component dominates. Thus Δν Nyquist,total=(Δν Nyquist,Analog + Δν 2 -2 Nyquist,Digital) . Note that if the analog Nyquist frequency is above the digital Độ tuyến tính, mã mất Nyquist frequency, aliasing will occur and data interpretation must include ADC có thể không chính xác la điều đương nhiên, ít nhất đầu ra của analysis of this effect. nó cũng thay đổi đều đều từ thấp tới cao khi đầu vào thay đổi từ thấp đến cao. Với chuyển đổi V-F, và đường dốc kép không gần 0V, ADC Linearity, missed codes tỏ ra không chính xác.Tuy nhiên, gần giá trị qua 0, với một vài đầu It is natural to expect that even if an ADC is inaccuracte, at least its output vào trên chuyển đôỉ xấp xỉ tuyến tính, một số khác trên chuyển đổi will change smoothly from low to high as an input changes from low to high. flash và do một số điều kiện khác trên hệ Σ-Δ bậc cao, đặc tính không For V to F converters, and for dual slope converters not near 0 volts, this đơn điệu có thể xuất hiện. Một ví dụ được chỉ ra như sau, trong đó bit expectation is met However, near zero cross-over, for some inputs on quan trọng thứ 3 của một thiết bị xấp xỉ liên tiếp có lỗi, nên ứng với sự successive approximation converters, for some flash converters, and for some thay đổi nhỏ cụ thể xác định ở đầu vào có bước nhảy tại đầu ra. conditions on higher order Σ-Δ units, non-monotonic behavior can occur. An example is shown below, where the resistor for the 3rd-least significant bit of a successive approximations unit has an error, so that there is a jump in output for certain specific small changes in input.

The linearity specification of an ADC is the root-mean-square difference between true linear response and the actual readout. One hopes the output is:

Count = Offset + k * Vin If there is continuously varying nonlinearity over the range of the converter, a better model for the output is: 2 Count = Offset + kL * Vin + kQ * V in For the situation we see in the graph above, the problem isn't large-scale nonlinearity, but rather discontinuities in the conversion. Here, simply Đặc điểm tuyến tính của một ADC là sự khác nhau căn bậc 2 giữa looking at the short-range slope of conversion per change in potential input phản hồi tuyến tính đúng và giá trị đọc ảo.. Đầu ra được mong đợi sẽ and comparing it to the overall average indicates that there's a patterned error. là:

Signal-to-noise ratio Đếm= Bù + k * Vin Ignoring all analog system errors and all nonidealities in the converter, the Nếu có tuyến tính biến thiên liên tục trải dải chuyển đổi thì đầu ra signal-to-noise ratio for a single reading of an N-bit ADC is 6.02 N + 1.76 đươc tính như sau: dB. Recall that 1 order of magnitude in POWER is 10 dB (decibels), while 1 Đếm= Bù + k * V + k * V2 order of magnitude in potential is 20 dB. dB is a logarithmic scale. L in Q in Assumptions in the 6.02 relationship include that the ADC dedicates 1 bit to Trường hợp trong hình trên, không phải là một phi tuyến tính dải lớn, sign, that the signal is sinusoidal, and that one is trying to determine the root mà là do không có sự liên tục trong chuyển đổi. Nhìn vào đường dốc mean square signal magnitude. It is perhaps easier to think of this in linear tầm ngắn của chuyển đổi trong mỗi biến thiên điện thế đầu vào và so terms, so S/N = 0.088×100.301 N. Thus, a 1 bit ADC (comparator) has an S/N of sánh nó với giá trị trung bình tổng thể , cho thấy có lỗi định mẫu. 0.176. This should bother the reader; a comparator that may be able to Tỉ số tín hiệu- nhiễu distinguish a potential change of a few microvolts is here claimed to have Bỏ qua tất cả các lỗi hệ thống analog, và tất cả điều kiện không lí S/N<1. In fact, there is no way to tell if one is looking at signal or noise with tưởng trong máy chuyển đổi, chỉ số tín hiệu-nhiễu cho1 số đọc N-bit just one bit; one must have several bits so that it is clear that the mean is của ADC 6.02 N + 1.76 dB. Nhớ rằng, 1 bậc độ lớn trong mũ là 10 dB significantly different than the noise. (decibels), trong khi đó độ lớn trong khi độ lớn của điện thế là 20 Using the 6.02 N formula, a 12 bit converter gives S/N = 360. Thus, while a dB,dB là hệ thập phân. Điều kiện trong quan hệ thức 6.02 bao gồm 12 bit ADC reads to 1 part in 4096, allowance for the sign cuts the magnitude :ADC cho 1 bit đánh dấu, tín hiệu là hình sine, và ta đang cố xác định measurement to one part in 2048, and the rest of the narrowing comes from căn bậc 2 độ lớn tín hiệu.Có thể đặt sẽ dễ hiểu hơn nếu đặt bài toán converting peak range to RMS. dưới dạng các khái niệm tuyến tính, khi đóS/N = 0.088×100.301 N. Vì A more realistic look at S/N takes into account the electrical noise in the thế, ADC 1bit (máy so mẫu) có tỉ lệ S/N là 0.176. Ta có thấy điều này ADC circuit and analog components feeding that circuit. In the absence of phiền toái;một máy so mẫu có thể phận biệt biến thiên hiệu điện thế cỡ analog noise, one has an uncertainty of 1 in the least significant bit (i.e. an vài micro volt có S/N<1.Trong thực tế, không làm thế nào biết được infinitesimal change to the analog signal might flip that bit between 0 and 1). với giá trị 1 bit thì đó là nhiễu hay tín hiệu, phải có tầm vài bit thì phân ADCs are sometimes specified to be accurate to ±1/2 LSB, meaning that the biệt được giá trị trung bình với nhiễu. potential at which the last bit "flips" from 0 to 1 (or vice versa) is always Dùng công thức6.02, chuyển đổi 12 bit cho S/N=360. Vì thế, trong khi within a potential range corresponding to the value digitized by that bit. For ADC 12 bit được được 1/4096, dung sai dấu chia số đo độ lớn tới example, if we have an 8 bit, straight binary converter with a 5.12 V range, 1/2048, và phần thu hẹp còn lại là do chuyển đổi dải peak sang RMS then the least significant bit corresponds to 5.12 V/256 = 0.02 V. As long as Xem xét S/N một cách thực tế hơn trong hiện tượng nhiễu điện của every count occurs within ±0.01 V of the potential where each transition is mạch ADC và các thành phaanf analog của mạch đó.Nếu không có expected, then S/N = 256. nhiễu analog, thì độ bất định là 1 trong các giátrij bit ít quan trong But now combine what the digitizing does with what the analog circuits are nhất( ví dụ: một thay đổi cực nhỏ trong tín hiệu analog có thể đảo doing. There is Johnson noise in the resistors, shot noise in the current, ngược bit đó giữa khoảng 0 và 1). Các ADC đôi khi được chỉ định độ thermal drift in everything. The result is that real ADCs have band-width chính xác tới±1/2 LSB, có nghĩa rằng hiệu điện thế mà tại đố bit cuôi dependent, external-circuit-dependent noise. Shown below is a signal đảo ngược từ 0 sang 1( hoặc ngược lại) luôn nằm trong một dải điện observed by a 16 bit ADC, recording data at 100 Hz. The second plot shows thế tương ứng với giá trị được số hóa của bit đó. Ví dụ, nếu có một the spectrum (Fourier Transform) of the first 4096 points. Rollovers will chuyển đổi 8 bit, nhị phân chuẩn với dải 5.2 V, thì bit ít quan trọng show larger versions of the plots: nhất ứng với. 5.12 V/256 = 0.02 V. Nếu có đếm trong phạm vi ±0.01 V của điện thế nơi có chuyển đổi, thì S/N = 256. Kết hợp kết quả số hóa với mạch điện. Có nhiễu Johnson trong điện trở, nhiễu hạt trong dòng điện, trôi nhiệt trong mọi thứ. Kết quả là The green line in the spectrum is for a fall-off in noise of 1/f, that is, thermal ADC thực phụ thuộc độ rộng của dải và có nhiễu phụ thuộc mạch điện drift. The total noise asymptote, the red line, sums 2.5 counts (RMS) per ngoài. Dưới đây là tín hiệu quan sát được bơi ADC 16 bit, dữ liệu ghi decade of frequency white noise with the 1/f noise. This is the same as saying ở 100Hz.Đồ thị 2 chỉ ra phổ của 4096 điểm đầu tiên ( Biến đổi that above 1 Hz, the 16 bit converter is operating at 13.5 effective bits (13.5 Fourier) Shown below is a signal observed by a 16 bit ADC, recording effective + 2.5 noise = 16), and below 1 Hz, the drift in the overall data at 100 Hz. measurement system results in higher noise.