Lecture 16 April 27, 2009 Asynchronous design

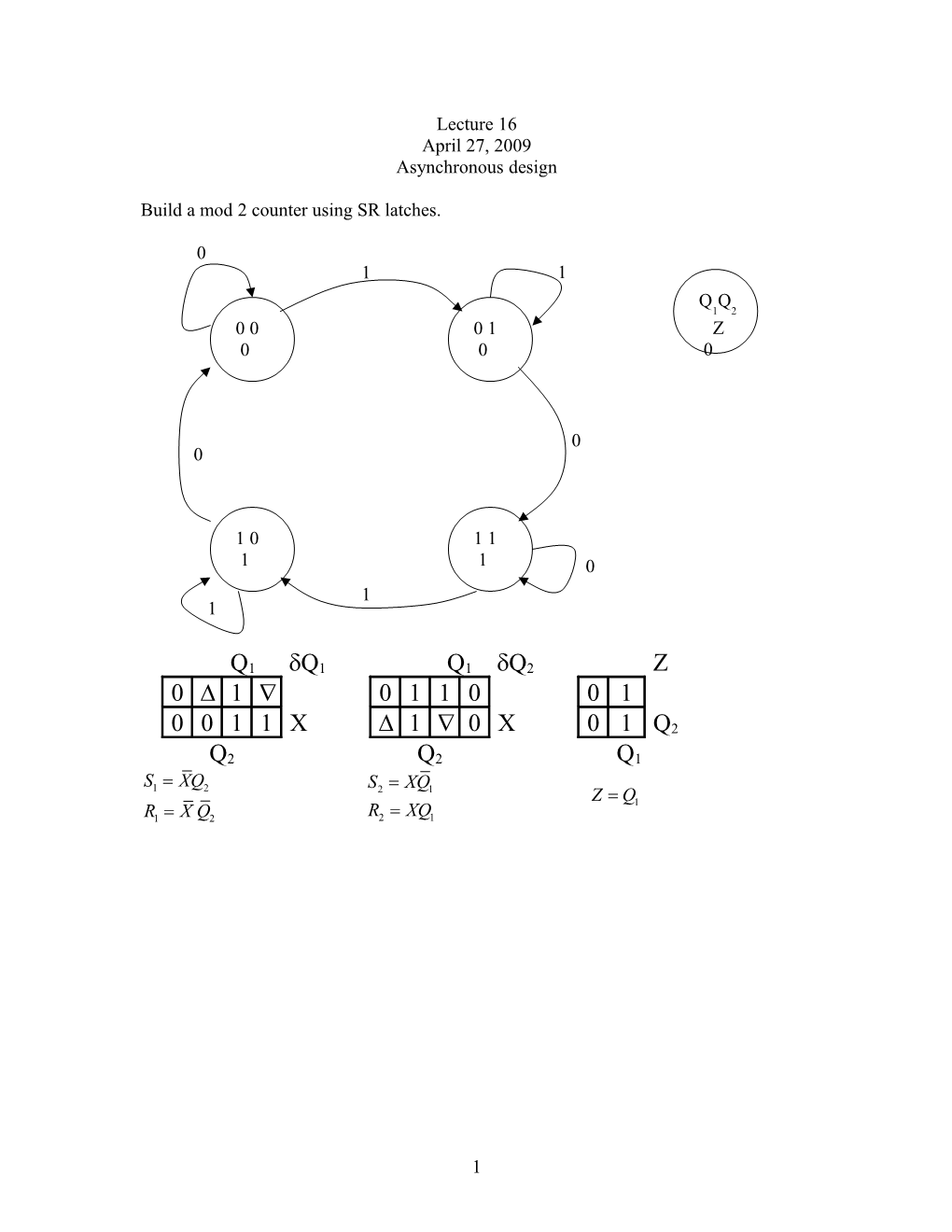

Build a mod 2 counter using SR latches.

0 1 1 Q Q 1 2 0 0 0 1 Z 0 0 0

0 0

1 0 1 1 1 1 0 1 1

Q1 Q1 Q1 Q2 Z 0 1 0 1 1 0 0 1

0 0 1 1 X 1 0 X 0 1 Q2

Q2 Q2 Q1

S1= XQ 2 S2= XQ 1 Z= Q1 R1= X Q 2 R2= XQ 1

1 Design of the master slave JK flip-flop 74LS73

KC

11 10 C /C 1 1 Q Q /K/C 2 1 Z /C /C

/J/C 01 00 0 0 C JC /C

C C J J Q2 0 0 0 0 0 0 0 0 0 0 0 0 Q1 Q1 1 1 1 1 1 1 1 1 Q2 Q2 1 1 1 1 K K

S2 CQ1 R2 C Q1 C C J J Q1 0 0 0 0 0 0 1 11 1 1 1 1 1 Q1 Q1 1 1 1 1 1 1 Q2 Q2 0 0 0 0 0 0 0 0 K K

S1 CJQ2 R1 CKQ2

2 S2 CQ1 R2 C Q1 S1 CJQ2 R1 CKQ2

Suppose J goes to 0 before C goes to 0.

3 True JK Flip-flop, 74LS107

The master slave JK flip-flop

4 True JK Flip-flop

5 Consider the above state assignment and what happens when the state changes form 10 to 01. We cannot expect both flip-flops to change exactly at the same time; therefore, depending on which flip-flop changes first we the FSM could go to state 00 or 11. If the FSM goes to 11 first it then goes to 00 and everything is all right. However, if the FSM goes to 00 first it will stay in 00.

6 7 Example #1. Design an asynchronous FSM with input X and Y and output Z. Z goes to 1 when X and Y are 1. Z goes to 0 when X and Y are 0. Otherwise Z does not change. Here we do not have a clock. Without a clock, we cannot design the machine as a synchronous finite state machine.

X

Y

Z

XY

X'+Y' Q=0 Q=1 X+Y 0 1

X'Y'

X Q 0 0 0 Q 1 1 1 Y

S (;d,1) XY, R (;d,0) X Y , Z Q We can also find an implementation using Q*. Q*(Q) ,1;d XY QX QY XY Q(X Y ) XYQX Y Q Draw the circuit.

8 Example #2 Design an asynchronous FSM with inputs X and Y and output Z. Z changes from 0 to 1 if Y changes from 0 to 1 when X = 1. Z changes from 1 to 0 when X returns to 0. X and Y will not change at the same time. Or: Design an asynchronous FSM with inputs X and Y and output Z. Z goes to 1 if Y when X = 1. Z remains 1 till X. X and Y will not change at the same time. i.e. Z = Z’XY, Z = ZX, XY = 0.

An experienced designer might implement this circuit as shown below1. 1

U5A 4 X 2 5 Z D R Q P Y 3 CLK

L 6

C Q 74LS74 1

Not being so cleaver, we will have to design the circuit as a asynchronous FSM.

Y XY'

X' S0 S1 XY' 0 0

X'Y'

X' XY

S2 1 X

XY 00 01 11 10 Z Wait for X=1, Y = 0 S0 S0 S0 S0 S1 0 Wait for Y S1 S0 - S2 S1 0 Wait for X S2 S0 S0 S2 S2 1

1 The commonly available formal methods do not provide the capability to create such a circuit. The Q techniques that we have studied coupled with my Boolean calculus could be used to develop formal methods for designing such circuits.

9 Consider the state assignment shown below.

XY

Q2Q1 00 01 11 10 Z Wait for X=1, Y = 0 00 00 00 01 00 0 Wait for Y 01 00 - 10 01 0 Wait for X 11 00 00 10 10 1

Y XY'

X' 00 01 XY' 0 0

X'Y' Q2Q1 Z X' XY

11 1 X

X Q2 X Q1 0 0 0 0 0 0 0

0 d0 0 d 1 1 Q1 Q1 1 1 1 1 Q2 Q2 d d d1 d1 d0 d0 d d Y Y

S2 XYQ1 S1 XY Z Q2 R2 X R1 X Note: Subscripts show what actually happens in don’t care conditions for this implementation. Does this circuit really work?

10 Watch out for things that go bump in the night! How can we avoid potential problems?

Consider the state assignment shown below.

Y XY'

X' 00 01 XY' 0 0

X'Y' X' X' Q2Q1 Z X' XY

10 X' 11 1 1 X

S2 XYQ1 S1 XY Z Q2 R2 X R1 X

Consider what happens when we are in state “11” and X goes to “0”. Q2 and Q1 will probably not both change to “0” at exactly the same time. Thus, we may go to state 01 or 10. Analysis proves that in case everything takes care of it self. We were lucky, but as engineers, we should not depend on luck.

11 My Rule: In asynchronous design, make the state assignment so that only one state variable changes that a time. Violate this rule only after careful analysis; such as we did above, to be sure that you are not going to get into trouble. How do you make a state assignment in the above example so that only one variable changes at a time? Answer: Add a new state to force the desired behavior.

Y XY'

X' 00 01 XY' 0 0

X'Y' X' Q2Q1 Z XY

10 11 X' d 1 X

Adding new states to enable a “unit distance” state assignment may require that we increase the number of state variables and thus increase the number of flip-flops.

My Rule: Avoid asynchronous design whenever possible. In asynchronous design, hazards are a source of concern. For additional information, read sections 7.9.1, 7.9.2, 7.93, and 7.9.4 in the book.

12 Asynchronous Machine Examples

Design an asynchronous finite state machine with inputs X and Y and output Z. If X went false last then Z = 1. If Y went false last then Z = 0. Thus, the output is set by X and reset by Y. You may assume that the initial value of Z is unimportant and X and Y will not change at the same time. X X X Y Z 0 1 Y Y

The state diagram requires four states.

X' X S0 X S1 0 0

XY' X'Y' X'Y' X'Y

S3 S2 1 Y 1 Y' Y

This state diagram accurately describes the machine, but how do we make the state assignment? To make a unit distance state assignment it would be necessary to add states. Implementation would require more than two flip-flops. Let’s try another approach. Consider an alternative state diagram.

X' X S0 X S1 0 0

Y' X'

S3 S2 1 Y 1 Y' Y

13 We can now make a unit-distance state assignment.

X' X 00 X 01 0 0

Q2Q1 Z Y' X'

10 11 1 Y 1 Y' Y

X Q2 X Q1 0 0 0 0 0 0 0 0 1 1 1 1 Q1 Q1 1 1 1 1 1 1 Q2 Q2 1 1 0 0 0 0 Y Y Using SR latches the equations are:

S2 XQ1 S1 XQ2 Z Q2 R2 Y Q1 R1 YQ2 If designed using NAND gates with feedback, the equations are: Q2 Q2 (,1;d) XQ1 Q2Q1 YQ2 XQ1 Q2Q1 YQ2

Q1 Q1 (,1;d ) XQ1 Q2Q1 YQ2 XQ1 Q2Q1 YQ2

14 Switch Bounce

U

D

Z

/UD UD UD 0 1 U/D /D - /U

U Q d 0 0 Q d 1 1 D

S U , S (Q) (0;d,1,) U Q R D, R(Q) (1;d,0,) D Q

15