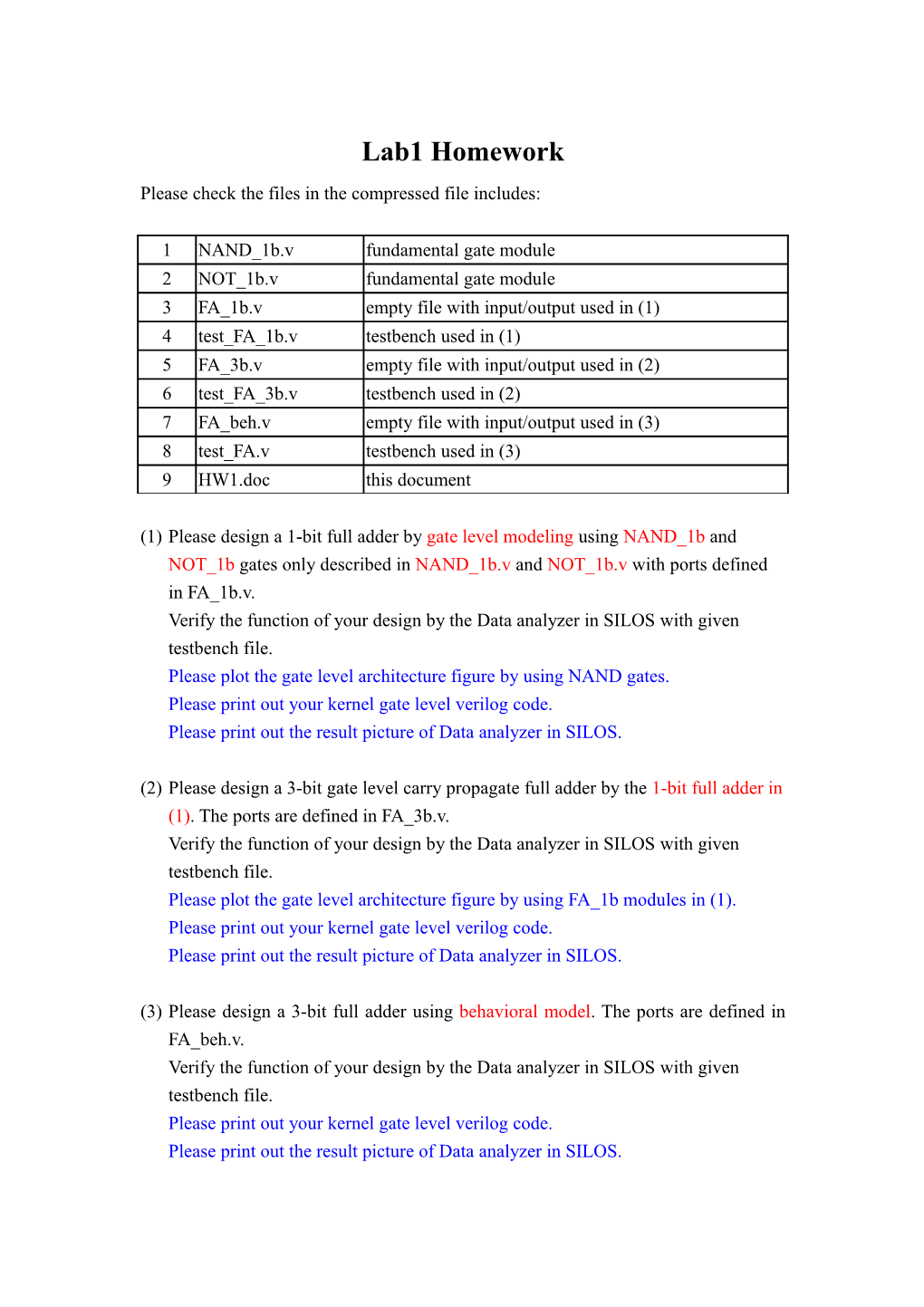

Lab1 Homework Please check the files in the compressed file includes:

1 NAND_1b.v fundamental gate module 2 NOT_1b.v fundamental gate module 3 FA_1b.v empty file with input/output used in (1) 4 test_FA_1b.v testbench used in (1) 5 FA_3b.v empty file with input/output used in (2) 6 test_FA_3b.v testbench used in (2) 7 FA_beh.v empty file with input/output used in (3) 8 test_FA.v testbench used in (3) 9 HW1.doc this document

(1) Please design a 1-bit full adder by gate level modeling using NAND_1b and NOT_1b gates only described in NAND_1b.v and NOT_1b.v with ports defined in FA_1b.v. Verify the function of your design by the Data analyzer in SILOS with given testbench file. Please plot the gate level architecture figure by using NAND gates. Please print out your kernel gate level verilog code. Please print out the result picture of Data analyzer in SILOS.

(2) Please design a 3-bit gate level carry propagate full adder by the 1-bit full adder in (1). The ports are defined in FA_3b.v. Verify the function of your design by the Data analyzer in SILOS with given testbench file. Please plot the gate level architecture figure by using FA_1b modules in (1). Please print out your kernel gate level verilog code. Please print out the result picture of Data analyzer in SILOS.

(3) Please design a 3-bit full adder using behavioral model. The ports are defined in FA_beh.v. Verify the function of your design by the Data analyzer in SILOS with given testbench file. Please print out your kernel gate level verilog code. Please print out the result picture of Data analyzer in SILOS. NOTE: The blue parts above are what should be put in your report. Please paste the kernel codes (added by you) and paste the result waveforms to the report file and submit it with hardcopy to the mailbox of TA, 莊子肇 in EE II building.

In this homework, the design of testbench is done by TA. Being a hardware designer, you have to write the testbench file for each hardware design. So if you are interested in testbench writing, please trace the three testbench files. They contain some basic usages of testbench syntax. . on-line learning of Silos, check this page http://www.simucad.com/silos_verilog_hdl/index.shtml useful website for learning Verilog http://www.cs.ucsd.edu/classes/sp02/cse291_E/CAD/resources.html