ECE 477 Digital Systems Senior Design Project Rev 3/12

Homework 9: Software Design Considerations

Team Code Name: AWESILLOSCOPE Group No. 2 Team Member Completing This Homework: Jintao Zhang E-mail Address of Team Member: zhang451@ purdue.edu

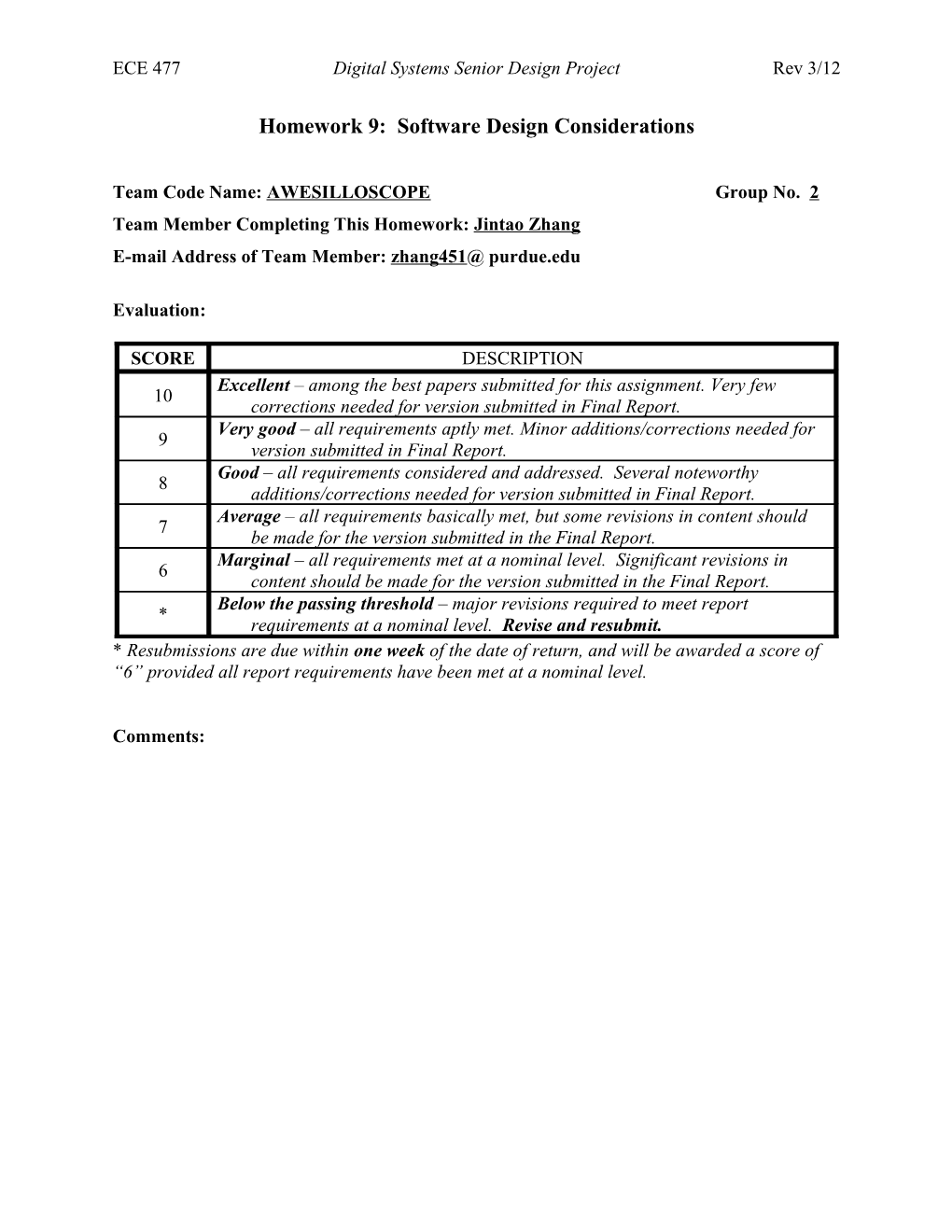

Evaluation:

SCORE DESCRIPTION Excellent – among the best papers submitted for this assignment. Very few 10 corrections needed for version submitted in Final Report. Very good – all requirements aptly met. Minor additions/corrections needed for 9 version submitted in Final Report. Good – all requirements considered and addressed. Several noteworthy 8 additions/corrections needed for version submitted in Final Report. Average – all requirements basically met, but some revisions in content should 7 be made for the version submitted in the Final Report. Marginal – all requirements met at a nominal level. Significant revisions in 6 content should be made for the version submitted in the Final Report. Below the passing threshold – major revisions required to meet report * requirements at a nominal level. Revise and resubmit. * Resubmissions are due within one week of the date of return, and will be awarded a score of “6” provided all report requirements have been met at a nominal level.

Comments: ECE 477 Digital Systems Senior Design Project Rev 3/21

1.0 Introduction The project we propose is a digital oscilloscope with playback function that provides almost any function of a typical oscilloscope, such as digital sampling, signal processing, scaling, cursor setting, reconstruction and visualization of signals. Additional features will be included, such as recording and replicating signals as a function generator, and writing data to external storage (SD card). Based on the functions required, the software will be split into 5 different sections: Sampling, Data-processing, Data-transmission (I2C), Display, and Output. The Sampling section contains the trigger-setup sequence and the data-retrieval sequence; the Data-processing section contains the FFT algorithm and calculation functions; the Data-transmission section contains the MCU I2C transmission function and FPGA I2C receiving function; the Display section is programmed and executed in the FPGA; and the Output section interacts with the USB and DAC interfaces to provide digital and analog output, respectively.

2.0 Software Design Considerations 2.1 Data Storage/ Memory Allocation Since the FPGA will only be implemented as a display unit and all crucial calculation/ data-processing will be performed in the MCU, it is critical to effectively manage the SRAM size for temporary storage and calculation. Additionally, sampling and processing data would certainly need a large amount of memory for arrays of variables, I/O registers, and buffers, so clearly defined memory location and the format of the data inside the MCU would be necessary. There are three categories of task for the MCU to complete, which are sampling, user interfacing, and calculation; accordingly, there are 3 major types of data required. First, for each of the two sampled channels, 480 data points with 12-bit resolution data would be required; the storage of these data points will take up a major portion of the allocated memory. Next, for each general purpose pushbutton input, a register (one bit of a structure, preferably) will be used as a flag. Register value will be set in the Interrupt, and then cleared in Main; following that the corresponding function will be executed. The USB_MODE register would be a toggle based register, since USB mode in the Main function has a higher priority than all other functions. The RPG register will be initialized as a signed value and repeatedly changed when rotational pulse is detected. Other necessary flags will also be defined with these flags. Last but not least, the

-2- ECE 477 Digital Systems Senior Design Project Rev 3/21 calculated results will be initialized as 0s and updated by the function. The display sequence will read all these and transmit them by pack to the FPGA. The microcontroller possesses an embedded SRAM of 192 Kbyte, split up into three blocks of 112 Kbyte, 64 Kbyte and 16 Kbyte. The start address of the SRAM is 0x2000 0000. Since the CPU is directly reading/writing from/to the 112 Kbyte SRAM (ends at 0x2001 BFFF), all the required flags, and registers mentioned above along with the stack pointer will be stored in this location. During execution, the SRAM will be accessed through the system BUS, so the flag and registers will be updated timely. Although the SRM32F40x series MCU have the capability to boot from SRAM by setting the BOOT [1:0] vector, it is decided that all the code will be stored and running in the FLASH memory, because FLASH will not lose memory when the power is cut-off, and it has a larger space than SRAM. So the booting mode of the microcontroller will be, by default, FLASH boot with available FLASH memory from 0x0800 0000 to 0x080F FFFF.

2.2 Function Implementation The Main function in the STM32 MCU will use flag-driven operation. Interrupts (majorly TIMER interrupt) will keep update data arrays and Main loop will perform flag-driven, real time analysis. Due to large amount of potential calculation (480 points FFT), TIMER interrupts will be temporarily disabled when FFT is taking place, which will cause the device get into “No response” state for a short period (~tenth of millisecond). Besides the Main function, 2 ADC channels, 4 TIMERs, and 1 DAC channel will be employed to perform necessary functions such as interrupting, sampling and output. The ADC sampling channel have its own clock and Phase-Lock Loop, after initialization, it will keep interrupting with the rate of 1.2 MHz (controlled by ADC_SMPR1) and keep updating the ADC_DR register. The trigger will always be setup with the fastest sampling rate; however the recorded data will be properly separated by sampling rate. TIMER1 will be used for detecting real-time general purpose input from user interface and set up corresponding flag; TIMER2 will be used for I2C data transmission, as mentioned beforehand, the FPGA will neither store nor process any data, it will simply translate the data from MCU into VGA display, therefore the MCU is controlling the refresh rate of the screen. The data will be send every 10 ms (100 Hz) to maintain the refresh rate (60 Hz). When data is

-3- ECE 477 Digital Systems Senior Design Project Rev 3/21 transmitting, it should not be interrupted by any other TIMER; otherwise the data transmission may be sabotaged. Therefore the priority of I2C should be the highest among all the TIMERs. TIMER3 and TIMER4 will perform two different kind of sampling, one is for “Fast sampling” and the other is for “Slow sampling”. Each will setup the trigger followed by retrieve certain points of data. For the “Fast” mode, 480 data points will be retrieved within 1 interrupt separated by delay functions, thus it requires the retrieval rate to be fast; the “Slow” mode will retrieve 1 data point at a time, but the interrupt rate will be determined by the sampling rate. DAC output, unlike the ADC, does not have a self-timer. Thus an additional TIMER would be utilized for the DAC trigger. The data ready to be output will be stored into DAC buffer and TIMER provides the proper “release rate” for the data array. The output circuitry will take care of the magnitude of the signal. When DAC is enabled, an additional TIMER interrupt will be added.

Code Priority

-4- ECE 477 Digital Systems Senior Design Project Rev 3/21

3.0 Software Design Narrative Overall, the Main function is a hybrid of polling and flag-driven structure. Within the Main function, different blocks will be implemented and they will perform different purposes. Also the Main function will keep check for the flags and perform corresponding sequences to clear the flags. Other than the Fast Sampling interrupt, all the other interrupts will not perform any major calculation. Therefore, in the Main function all the priority levels and the execution chain order will be determined. Other than the Main function, 4 additional TIMER interrupts will be used for Slow Sampling, Fast Sampling, general purpose input-check, and display update purposes, respectively. GP input-check will simply perform routine edge-detection on each pushbutton and RPG. Other interrupt sequences are described below.

3.1 MCU Code, Interrupts Slow Sampling (TIMER successfully configured, code not yet started): In Slow sampling mode, the TIMER interrupts at the sampling rate. If the trigger is not set yet, 3 points will be retrieved and compared with the 3 initial values for trigger setup. Every time a new set of data is fetched before trigger is set, timeout counter will be incremented. If the trigger is set or timeout counter exceeds its maximum value, the sampling sequence will not attempt to setup the trigger. Instead, a data-point will be fetched and stored in the data-array. When the data-array is filled, the trigger will be reset and the sampling sequence will start-over. Fast Sampling (Not yet started): In Fast sampling rate mode, same trigger setup sequence will be implemented at each TIMER interrupt. If the trigger is not set, it will keep fetching data in the same TIMER interrupt. After timeout or trigger is set, 480 data-points will be retrieved separated by delay function to satisfy user’s sampling time setting. I 2C Data transmission (Finished and tested): The VGA should keep refresh with minimum 60 Hz frequency. Thus the MCU should update the data transmitted to FPGA frequently. Therefore every 10 ms, MCU will send a new data package to FPGA in order to update the display. The reason to keep a 100 Hz refresh rate is to guarantee the update rate can be stabilized at 60 Hz.

-5- ECE 477 Digital Systems Senior Design Project Rev 3/21

3.2 MCU Code, Main Peak to Peak value calculation (Status: Not yet started): The algorithm to find the maximum and minimum point of the fetched data points is Bubble Sort. As there are only 480 points for sorting, Bubble sort will be efficient and fast enough to complete the task. Frequency and Period Calculation (Status: FFT code already processed, others not yet started): With all 480 points sampled and stored, a “data_complete” flag will be triggered. If user requests frequency and period information at this point, the calculation sequence will perform a high-priority Fast Fourier Transform to the data-points. After DFT magnitudes are acquired, the maximum value will be acquired and corresponding frequency will be calculated based on current sampling frequency and maximum frequency position. After the frequency is calculated, the period will be fairly easy to calculate. Offset (Not yet started): The offset function, if triggered by user, will add the certain amount offset value to every data-point based on corresponding RPG data register, thus the entire data sequence displayed will be shifted accordingly. Sampling Frequency Change (Not yet started): By default, the sampling frequency will be 1 kHz (1ms separation in “slow” sampling mode). User can change the sampling frequency by selecting it in the RPG menu and then rotate the RPG. The updated sampling frequency data will effectively change the TIMER interrupt rate (slow mode) or the delay sequence between fetching data point (fast mode), respectively; the same value will also be used in frequency/ period calculation. Run/ Stop (Not yet started): The run/stop function will be used to freeze the display waveform (but the sampling and menu will keep running). Therefore, the data-points will be “locked” when run/ stop flag is cleared. However, it will affect neither the sampling sequence nor the user interface. User can still analyze the static data-points with internal functions. User presses the button again to resume normal function and dynamic waveform. Scaling Calculation (Not yet started):

-6- ECE 477 Digital Systems Senior Design Project Rev 3/21

In case that user would like to view the data in a different horizontal or vertical scale, RPG menu can be used to set the scale factor. The scale factor (1, by default) will be multiplied to all data-points before the points being transmitted to FPGA display. The scale factor itself will also be transmitted in order to display the proper Voltage/ division and Time/ division values. Cursor Display (Not yet started): User can also view the exact location at any point of the screen via cursor. When cursor is enabled, it will by default appear in the center of the screen. Each RPG pulse will cause the cursor to move exactly the same distance on the screen (not necessarily same time/ voltage division). The cursor position vector will be updated as the cursor is moving around; the position vector will be displayed on the screen also when the cursor is enabled (by default, at (0, 0)). USB r/ w mode (USB writing sequence functioning, reading sequence still in progress): When the MCU interacts with the USB device for reads/ writes data, all other function will be temporarily disabled except the display function. The MCU will perform read or load from the external storage device. In read mode, the display will show the waveform stored in SRAM read from the USB device. Replay function (DAC tested, not related with TIMER yet): When the user saves a waveform, the MCU will store the data-points of a channel and its corresponding sampling frequency into the SRAM. When the user decides to replay the data stored in SRAM, the DAC will continuously output the corresponding data-points based on sampling rate.

3.3 FPGA Logic I2C (Code complete, not yet tested on FPGA): The FPGA will act as a slave device and receive data package from MCU in a specific format (sampling data, calculation results, and user interface info and cursor position). Since the MCU will be the only master and FPGA the only slave, no major feedback signals are necessary to be sent from the FPGA to the MCU except ACK and NACK signals. The data package will not be stored; instead will directly connect to display as the FPGA receives data. VGA display (Code partially completed, testing with certain patterns): The VGA will enable a 640*480 pixel resolution display. The screen is scanned line by line to update the pixel RGB data. Horizontal sync and Vertical sync signals are used to set up the

-7- ECE 477 Digital Systems Senior Design Project Rev 3/21 correct timing for scanning the screen. The display will include both the menu view and the data waveform. Each individual menu item will reverse color to indicate user selection.

4.0 Summary In conclusion, there are multiple difficulties in coding the Awe-silloscope considering the complexity of functions, algorithms, and transmissions. Several mode for sampling (Fast and Slow) and for main (USB mode and Normal mode) are required for specific functionality. Thus plenty of flags and registers will be implemented to create the polling structure of the Main code. Even though the majority of the code has not been completed, the theoretical ideas of all the functions are determined. We will focus on execute the plans in the next few weeks.

-8- ECE 477 Digital Systems Senior Design Project Rev 3/21

List of References

[1] STMicroelectronics (2011). RM0090 Reference Manual, STM32F405xx, STM32F407xx, STM32F415xx and STM32F417xx advanced ARM-based 32-bit MCUs [Online], Available on: http://www.st.com/internet/com/TECHNICAL_RESOURCES/TECHNICAL_LITER ATURE/REFERENCE_MANUAL/DM00031020.pdf Retrieved Mar. 21st, 2012

[2] STMicroelectronics (2011). Application Notes [Online], Available on: http://www.st.com/internet/mcu/product/252140.jsp, Design Support tab. Retrieved Jan. 17th, 2012

-9- ECE 477 Digital Systems Senior Design Project Rev 3/21

Appendix A: Flowchart/Pseudo-code for Main Program

Fig A.1 Main flowchart

Fig. A.2 Timer 1 flowchart

-10- ECE 477 Digital Systems Senior Design Project Rev 3/21

Fig. A.3 Timer 2 flowchart

Fig A.4 Timer 3 flowchart, Fast Sampling

-11- ECE 477 Digital Systems Senior Design Project Rev 3/21

Fig A.4 Timer 4 flowchart, Slow Sampling

-12- ECE 477 Digital Systems Senior Design Project Rev 3/21

Appendix B: Hierarchical Block Diagram of Code Organization

-13-