Comit Systems, Inc.

I2C MASTER CONTROLLER Product Description 1.0

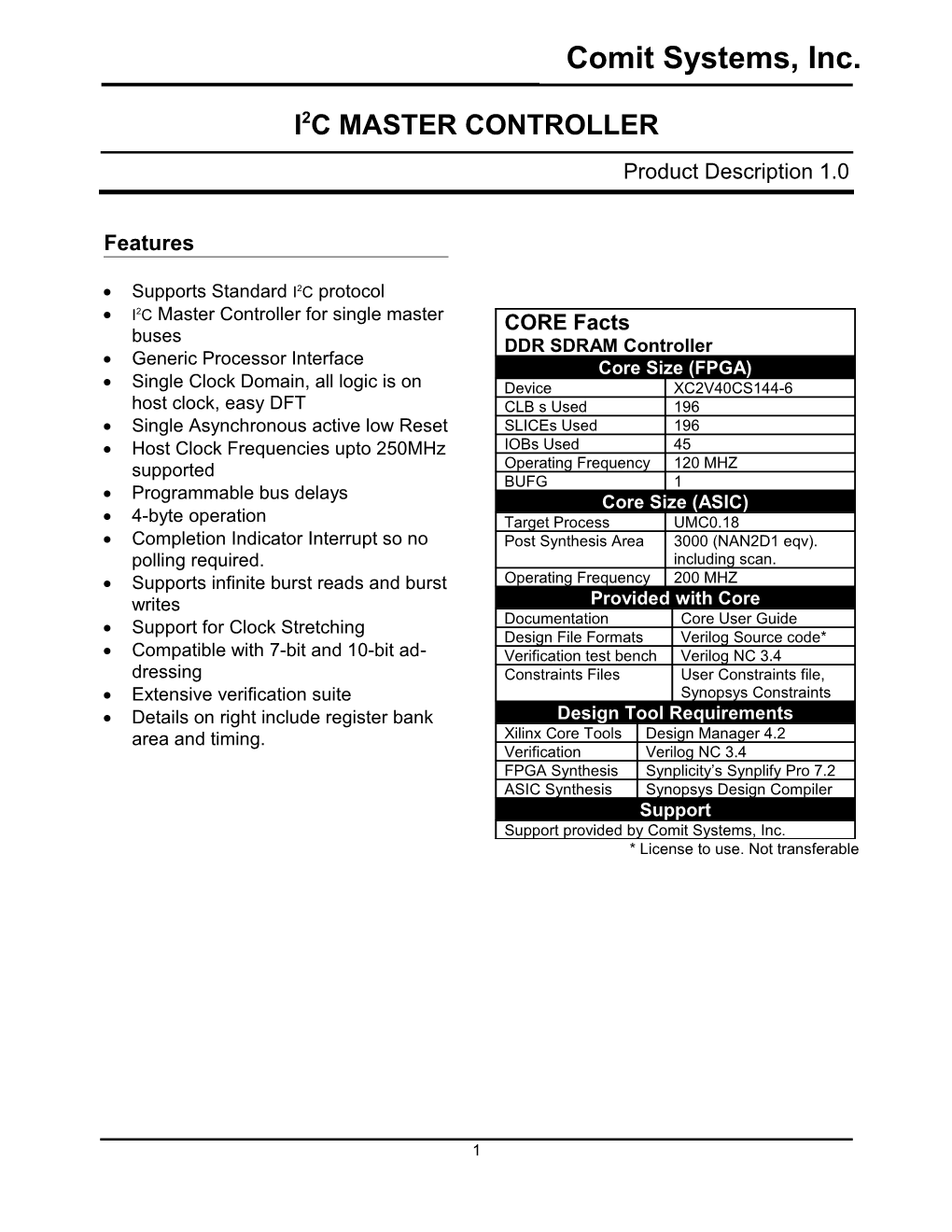

Features

Supports Standard I2C protocol 2 I C Master Controller for single master CORE Facts buses DDR SDRAM Controller Generic Processor Interface Core Size (FPGA) Single Clock Domain, all logic is on Device XC2V40CS144-6 host clock, easy DFT CLB s Used 196 Single Asynchronous active low Reset SLICEs Used 196 Host Clock Frequencies upto 250MHz IOBs Used 45 supported Operating Frequency 120 MHZ BUFG 1 Programmable bus delays Core Size (ASIC) 4-byte operation Target Process UMC0.18 Completion Indicator Interrupt so no Post Synthesis Area 3000 (NAN2D1 eqv). polling required. including scan. Supports infinite burst reads and burst Operating Frequency 200 MHZ writes Provided with Core Support for Clock Stretching Documentation Core User Guide Design File Formats Verilog Source code* Compatible with 7-bit and 10-bit ad- Verification test bench Verilog NC 3.4 dressing Constraints Files User Constraints file, Extensive verification suite Synopsys Constraints Details on right include register bank Design Tool Requirements area and timing. Xilinx Core Tools Design Manager 4.2 Verification Verilog NC 3.4 FPGA Synthesis Synplicity’s Synplify Pro 7.2 ASIC Synthesis Synopsys Design Compiler Support Support provided by Comit Systems, Inc. * License to use. Not transferable

1 Comit Systems, Inc.

haddr[3:0] scl_out hdata_in[15:0] scl_in hdata_out[15:0] hread i2c hwrite master hclk sda_out hreset_n sda_in hbe[1:0] hint

Figure 1. I2C Top Level

Recommended Applications The I2C master generates an interrupt on the 2 The I2C Master can be used for any application completion of every operation on the I C bus. requiring control of one or more I2C slave devices. This relieves the processor from polling the regis- ters to detect completion. Detailed completion General Description status is available in the registers. 2 The I C Master is written in such a way so as to On the Bus Side, there is only one output provid- be timng configurable. A configuration register ed for SCL and SDA each as they are open drain. 2 provides for the I C interface to run at a program- There is no filtering done inside the core on the mable fraction of the host clock speed. SCL and SDA inputs.

Functional Description Each operation is completely configurable in soft- ware, thereby allowing for compatibility with a The I2C master as delivered includes a register wide variety of I2C devices. bank for a 16 bit syncrhonous host bus. The documentation for the register bank is included in In particular 7 bit and 10 bit addressing is support- the deliverables. This register bank module is at ed. Any number of address bytes is supported. the top level of the I2C master, and can be re- placed if necessary. Comit can also deliver regis- Burst data transfers (read and write) of any length ter banks with different configurations as an are possible without restarting transactions. added-on service.

2 Comit Systems, Inc. Verification

The I2C master has been verified with multiple models. Timing analysis has been done using Primetime for asic.

The test bench will be provided as part of the de- liverables.

For CVXT users, there’s also an I2C model that is available. CVXT compatible register definitions will also be provided.

Comit Systems, Inc. 3375 Scott Blvd. Ste 139 Santa Clara, CA 95054, USA. Phone: +1 (408) 988-2988

URL: http://www.comit.com

3