CMPEN275 – Digital Design Lab Lab10 – FSM Penn State Erie, The Behrend College

1 Discussion The purpose of this lab is to modify a finite state to light the LEDs on the PLDT-3’s bar graph in a sequence. A simplified version of this project is provided to you. Your first task will be to analyze the VHDL code so that you understand the operation of the datapath as well as understand how a state diagram is coded into VHDL. The datapath and control unit are combined together in the lab10 entity given in Listing 1.

entity lab10 is port( reset, clk, but: in std_logic; bar: out std_logic_vector(7 downto 0)); end lab10;

Listing 1: The entity description of the Lab10 component.

The Lab10 circuit monitors the button input and cause the LEDs on the bar graph to light up in a sequence when the button is pressed and stop moving when the button is pressed again. The datapath contains a clock divider and an up/down counter. You will elaborate the details of their arrangement in the prelab. The FSM examines the push button and the output from the clock divider and up/down counter and control the clock divider and up/down counter based on the information that it recieved from these inputs. The entity description of the control unit is given in Listing 2.

entity fsm is port( clk, rst: in std_logic; but: in std_logic; sw: in std_logic_vector(2 downto 0); cw: out std_logic_vector(3 downto 0)); end fsm; Listing 2: The control unit for the Lab10 component.

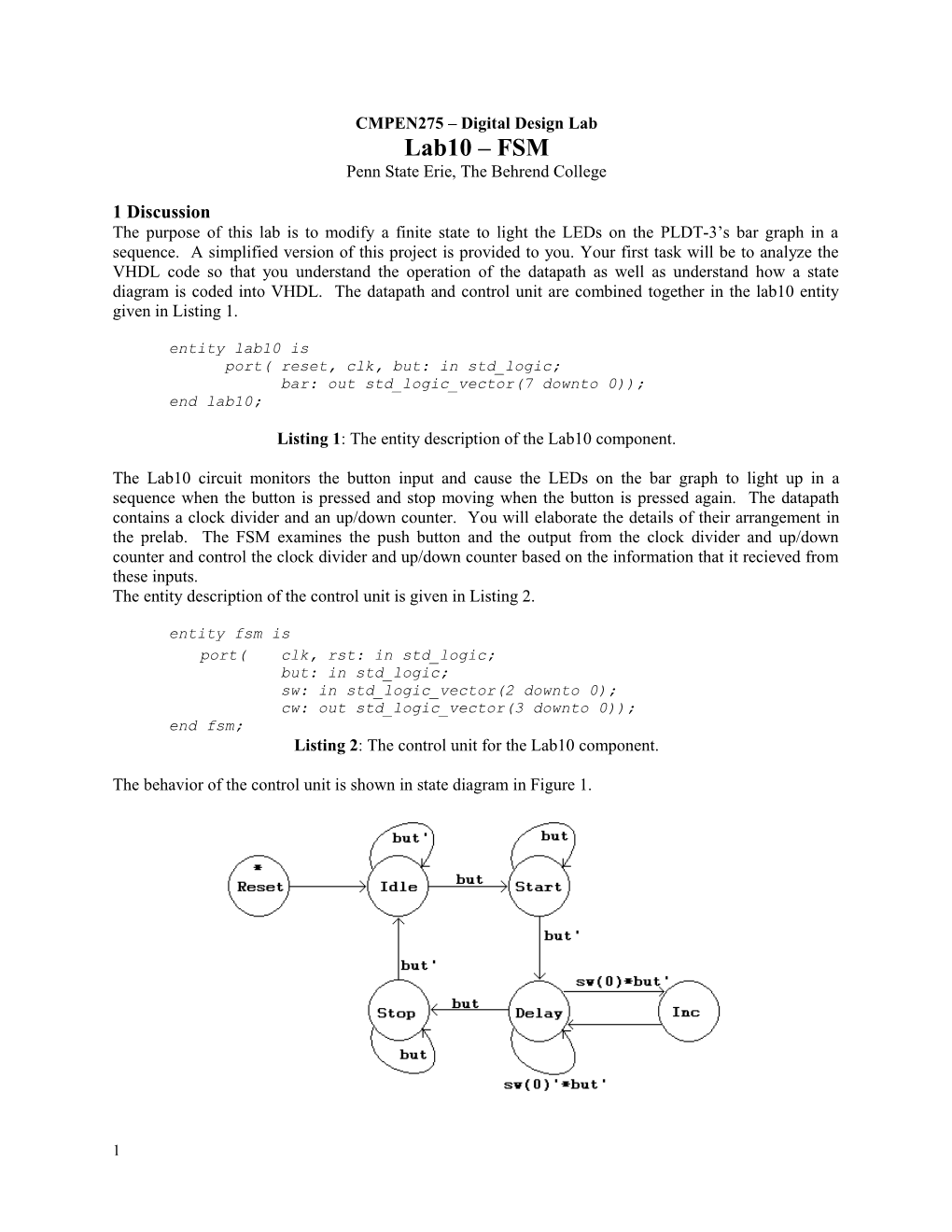

The behavior of the control unit is shown in state diagram in Figure 1.

1 32 Laboratory 7

Figure 1: The state diagram for the Lab10 control unit. The behavior of the control unit is as follows. The FSM starts in the Reset state (thats why its state circle has a * in it). The FSM immediatly goes into the Idle state where it waits for a button press. When the button is pressed by the user, the FSM moves to the Start state, where it waits for the button to be released. Once the button is released, the FSM goes to the Delay state, where it starts up the clock divider and waits for a tenth of a second to elapse. The sw(0) bit will go to logic 1 when a tenth of a second has elasped. If the button has not been pressed and a tenth of a second has elapsed, then the FSM goes to the Inc state. In the Inc state the FSM does two things, it clears the clock divider for the next tenth of a second delay and it increments the up/down counter cause the pattern on the bar graph to change. The FSM immediatly leaves the Inc state and goes back to the Delay state. If the button is pressed and the FSM is in the Delay state then the FSM goes to the Stop state. The FSM waits in the Stop state until the button is reased and then goes into the Idle state. At this point the button pressing cycle can begin again.

2 Prelab

1. Draw a schematic of the datapath described by datapath.vhd. 2. Complete Table 3, describing the effect each state’s control word should have on the datapath.

State Action Reset Idle Start Delay Inc Stop Table 1: The effects of control word bits in the datapath.

3. Complete Table 2. First, determine the effect of the control words bits on their respective components in the datapath. For example, when cw(3:2)=10 the counter in the datapath will count up. Next examine determine the control word settings for each state using Figure 1 and the subsequent discussion.

State cw(3:2) cw(1:0) counter updown 00 00 01 01 10 count up 10 11 11 Reset Idle Start Delay Inc Stop Table 2: The control word table for the Lab10 component.

2 4. Table 3 describes some control words setting to the datapath and the current value of some signals. From this determine the next value of the signal and the current value of the status word. Assume that tenth is set to 500,000.

cw Signal Current Value Next value Current sw(3,2,1,0) timer 123,456 1111 cnt 6 timer 123,456 1000 cnt 6 timer 123,456 0000 cnt 6 timer 500,000 1110 cnt 7

Table 3: The effects of control words on the signals in the datapath.

5. Create a pattern of LEDs on the LED bar graph that you would like to see displayed. Color in LEDs which are illuminated. In Table 4 record the binary code for the pattern, coding an illuminated led as a 1 with the leftmost LED as the MSB. Patter Binary Code n 0 1 2 3 4 5 6 7

Figure 2: LED patterns Table 4: The LED pattern codes.

6. Describe the modifications necessary to the VHDL files to produce the pattern of LEDs generated in question 5.

3 In-lab 1. Modify state_process in fsm.vhd to operate according to the state diagram in Figure 1

3 32 Laboratory 7

2. Modify the output_process in fsm.vhd to operate according to the control word you created in Table 2. 3. Modify the fsm entity description so that it’s consistent with that in the lab10 component description. 4. Simulate your design using the modified testbench. Produce a timing diagram with the following signals from top to bottom: reset, clk, but, downbut, (bouncebut), state, cnt, bar, sw(0) (just this 1 bit), timer[23:0] in hex. You will have to transcend the design hierarchy in order to get some of the signals. Your simulation will require about 3uS to complete, so press the “Run for the time specified on the toolbar” button a couple of times. 5. Create a UCF file using the resources on the PLDT-3 board. You can use pins 53 and xx as the button inputs. 6. Synthesize and test the accuracy of your project. **Bonus 10 pts** Create a state diagram for a FSM with an up and down button. When the up button is pressed the FSM should produce a light pattern which counts up from 0 to 7 and back to 0 again. When the down button is pressed the FSM should produce a light pattern which counts down from 7 to 0 and back to 7. Note, the initial value of the counter is unimportant. Furthermore, the updown counter automatically rolls over from 7 to 0 when counting up and from 0 to 7 when counting down.

***Bonus 10pts*** Add a third variation, the bounce button. When pressed it causes the FSM to count up to 7 and then down to 0 and then back up to 7, etc. Your FSM will have to use the min and max outputs of the updown counter to know when to switch counting directions.

4 Lab Report Each team of two students will turn in a single lab report. It should contain the following. Standard cover page with the following rubric.

Percentage Score PreLab 30 Simulation 30 Synthesis 40 Bonus 20

Two timing diagrams, one for the original fsm and one for the modified fsm. VHDL code for the architecture of the FSM.

4