Tutorial 2

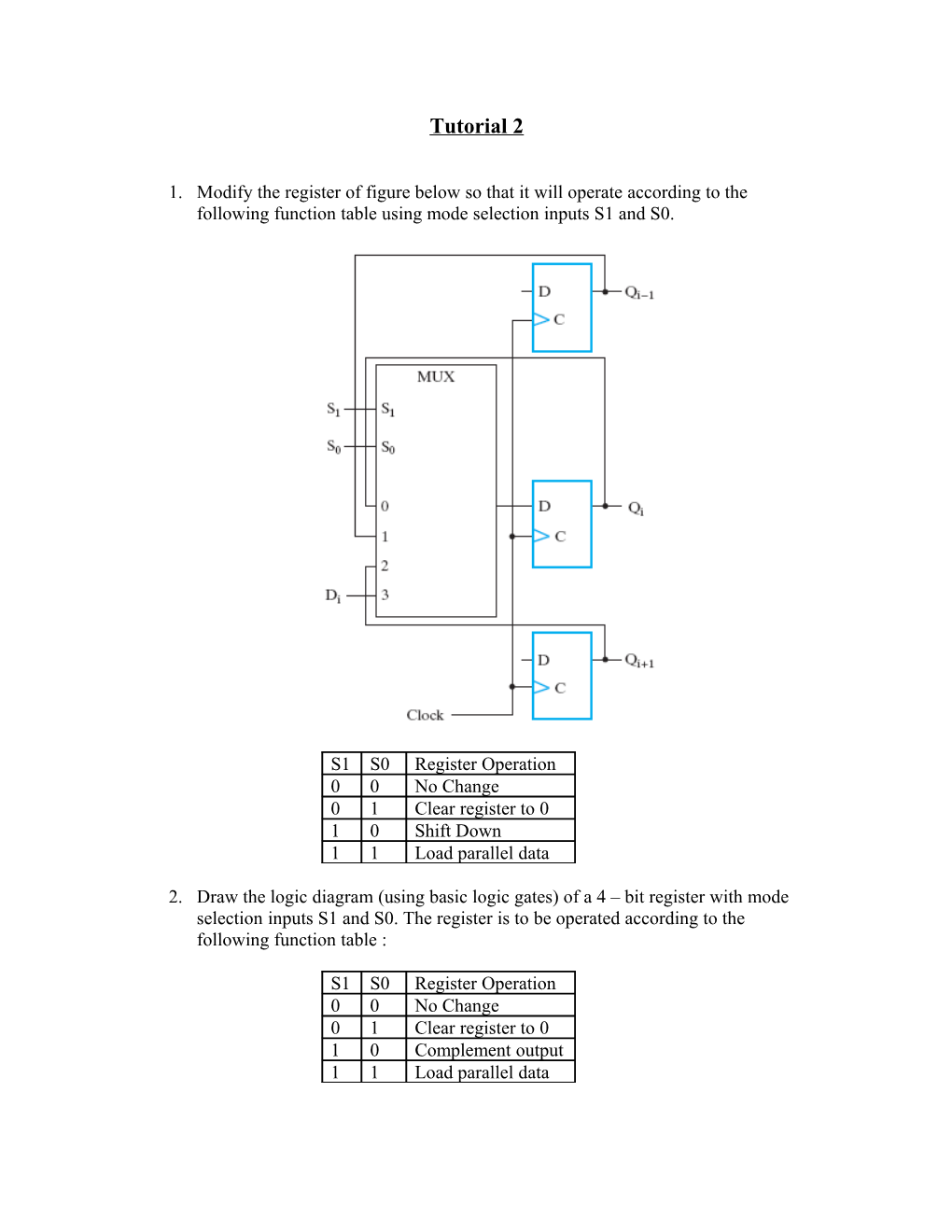

1. Modify the register of figure below so that it will operate according to the following function table using mode selection inputs S1 and S0.

S1 S0 Register Operation 0 0 No Change 0 1 Clear register to 0 1 0 Shift Down 1 1 Load parallel data

2. Draw the logic diagram (using basic logic gates) of a 4 – bit register with mode selection inputs S1 and S0. The register is to be operated according to the following function table :

S1 S0 Register Operation 0 0 No Change 0 1 Clear register to 0 1 0 Complement output 1 1 Load parallel data 3. Show the diagram of the hardware that implements the register transfer statement

C3 : R2 R1, R1 R2

4. A system is to have the following set of register transfers, implemented using buses :

C1 : R0 R1 C2 : R3 R1, R1 R4, R4 R0 C3 : R2 R3, R0 R2 C4 : R2 R4, R4 R2

a) For each destination register, list all of the source registers. b) For each source register, list all of the destination registers. c) With consideration for which of the transfers must occur simultaneously, what is the minimum number of buses that can be used to implement the set of transfers? Assume that each register will have a single bus as its input. d) Draw a block diagram of the system, showing the registers and buses and the connections between them.

5. Using two 4 – bit registers R1 and R2, together with AND gates, OR gates, and inverters (NOT), draw one bit slice of the logic diagram that implements all of the following statements :

C0 : R2 0 Clear R2 synchronously with the clock C1 : R2 R2 Complement R2 C2 : R2 R1 Transfer R1 to R2

Assume that : i) The control variables are mutually exclusive (only one variable can be 1 at any time) ii) No transfer into R2 will occur when all control variables are 0.

6. A register cell is to be designed for an 8 – bit register A that has the following register transfer functions :

C0 : A A B C1: A A B

Find optimum logic using AND, OR, and NOT gates for the D input to the D flip- flop in the cell. 7. A register cell is to be designed for an 8 – bit register R0 that has the following register transfer functions : S1 S0 : R0 0 S1 S0 : R0 R0 R1 S1 S0 : R0 RO R1 S1 S0 : R0 R0 R1

Find optimum logic using AND, OR and NOT gates for the D input to the D flip- flop in the cell.