YOU Can BUILD a SMARTER PLANET

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

AD112 Development and Deployment of Lotus Product Documentation Wikis

AD112 Development and Deployment of Lotus Product Documentation Wikis Craig Lordan | Manager Kevin Giles | Advisory Software Engineer 2 12 Agenda 11 1 10 2 ● Background 9 3 ▬ IBM Lotus® product wikis overview 8 4 ▬ 7 5 Your speakers today 6 ▬ IBM Lotus® Domino® infrastructure ● Lotus Domino wiki application development ▬ First pass at Lotus Domino wikis ▬ Benefits of XPages for wikis ▬ XPages Wiki template on OpenNTF ▬ Custom development examples ● Real-world experience ▬ XPages deployment experience ▬ Our XPages lessons ▬ What about wikis in IBM Lotus® Connections? ● Project future ● Q&A 3 Lotus product wikis overview ● Product wikis for all Lotus and IBM WebSphere® Portal products ● Live on the Internet, open to all customers and users ▬ Visit www.lotus.com/ldd/wikis ● Added first wiki for IBM Lotus® Notes® and Lotus Domino in December 2007 ● Additional wikis added in 2008 ● Current content includes supplemental technical content and IBM Redbooks® Wiki listing IBM Composite Applications IBM Lotus Notes ● IBM LotusLive™ IBM Lotus Notes Traveler Plan is to use wikis for official product IBM Mashup Center IBM Lotus® Quickr IBM Lotus® ActiveInsight® IBM Lotus® Sametime® documentation Lotus Connections IBM Lotus® Symphony Lotus Domino IBM Lotus® Web Content ▬ IBM Lotus Domino Designer Management IBM Lotus® Expeditor, IBM Lotus® Foundations, Lotus Expeditor IBM Lotus® Workforce Management IBM Mashup Center already publish product doc to IBM Lotus® Forms IBM WebSphere Dashboard Lotus Foundations Framework wikis IBM Lotus® iNotes® WebSphere Portal IBM Lotus® Mobile Connect IBM WebSphere® Portlet Factory 4 Your speakers today ● Craig Lordan, Manager ▬ Craig Lordan is a manager at IBM Lotus. He joined Lotus in 1998 as a technical writer for Lotus Notes and Lotus Domino. -

DB2 10 for Z/OS – a Smarter Database for a Smarter Planet How to Have a Happy DB2 CM

DB2 10 for z/OS – A Smarter Database for a Smarter Planet How to Have a Happy DB2 CM Day Triton Consulting The Royal 25 Bank Plain Norwich NR2 4SF Tel: 0870 241 1550 Fax: 0870 241 1549 email:[email protected] Introduction A lot has been said, written and presented regarding the many benefits and enhancements offered by DB2 10 for z/OS. Many DB2 sites are in the process of building cost cases to get management approval for the upgrade, or working with the business to agree implementation dates to minimise application impact. Other customers are deliberately building a delay into their implementation plans in order to allow the DB2 10 codebase to further mature before committing themselves. Whatever the reason, many of you are looking at dates for the initial upgrade to DB2 10 Conversion Mode (CM) that are many months, perhaps even years, away. That delay can sometimes be frustrating from a technical perspective, but there is a significant amount of preparation work you can be doing well in advance of “CM Day” for any given DB2 environment. This article outlines the major opportunities for preparation in advance of the move to DB2 10 Conversion Mode. Some of these changes require a full or partial outage, but if you are able to implement all or most of them as part of your routine maintenance activities, you will greatly reduce the risk and the elapsed time of the actual upgrade process - especially important if you are considering a skip-release upgrade from DB2 V8 to DB2 10. -

Education for a Smarter Planet: the Future of Learning CIO Report on Enabling Technologies

Front cover Education for a Smarter Planet: The Future of Learning CIO Report on Enabling Technologies Redguides for Business Leaders Dr. Jim Rudd Christopher Davia Patricia Sullivan Guidance to aid CIOs in strategic investment efforts The value of consumer IT, open platforms, and cloud computing in the future of education Practical examples of how enabling technologies are used today Introduction This IBM® Redguide™ publication is a supplement to the Future of Learning: Executive Insights Report. It provides an in-depth investigation into three enabling technologies and provides actionable guidance to aid CIO strategic and investment planning efforts. Specifically it discusses the value and role of consumer IT, open technologies, and cloud computing in the future of education. In addition, this guide provides real-world examples of the how these technologies work. This guide includes the following topics: Executive overview Exploring the technologies that enable the educational continuum Consumer IT Open platforms Cloud computing Creating Education for a Smarter Planet A roadmap for enabling a future vision Other resources for more information © Copyright IBM Corp. 2009. All rights reserved. 1 Executive overview Over the next decade, educational institutions will face significant change, transforming their relationships with students, teachers, and the workers of tomorrow. Signposts for the future are already visible, signaling significant changes to all segments of education as well as to their funders. These five signposts, which are technology immersion, personalized learning paths, knowledge skills, global integration, and economic alignment, are rapidly converging to produce a new and transformative paradigm that we call the educational continuum. This continuum dissolves the traditional boundaries between academic levels, education providers, and economic development initiatives to provide a single system for life-long learning, skills development, and workforce training. -

Smarter Planet” Business Strategy? Understanding How Data and Systems Are Used and Are Interconnected

Chapter 2 Case Assignment: David Plotkowski 000415004 1. What is IBM’s “ Smarter Planet” business strategy? Understanding how data and systems are used and are interconnected. As a forward thinking company and wise use of market orientation, IBM has the means to collect and analyze this data and understand how the world works along with all the available intelligence and continues to improve and provide tools an services and systems to improve living, communicating, educating, and healthy growth. From a marketing perspective, the IBM strategy focuses data technology and bringing together contrasting systems for the benefit of benefit its customers, the organization, its stakeholders, and society at large. How does this strategy relate to IBM’s mission and values? IBM continues to hold its 3 core values over a 100-year timespan regardless of changes in strategy or expression. The three core values are dedication to every client’s success, trust and personal responsibility in all relationships, and innovation that matters, for our company and the world. The Smarter Planet strategy easily defines and supports the core values. As people, devices and things connect, IBM sought through their core values to pull together the vast amounts of information to build better interconnectivity and defined their “Smarter Planet” strategy to benefit the world at large. The vision and foresight to embrace a need for interconnectivity provide new marketing opportunity for the “globally integrated enterprise.” IBM also has sold off other lines of business to focus on the core competencies, which kept them both competitive and well known over the past 100 years. -

Q1 Business Update

Q1 Business Update This presentation has been prepared by Animoca Brands Corporation Limited (“AB1”) as a summary only, and does not contain all information about AB1’s assets and liabilities, financial position and performance, profits and losses, prospects, and the rights and liabilities attaching to AB1’s securities. Some of the statements contained in this report are forward looking statements. Forward looking statements include but are not limited to, statements concerning AB1’s business plans, expected costs, and expected revenues, and other statements which are not historical facts. When used in this presentation, and in other published information of AB1’s, the words such as “aim”, “could”, “estimate”, “expect”, “intend”, “may”, “potential”, “should” and similar expressions are forward-looking statements. Although AB1 believes that its expectations reflected in the forward-looking statements are reasonable, such statements involve risk and uncertainties and no assurance can be given that actual results will be consistent with these forward-looking statements. AB1 does not purport to give financial or investment advice. No account has been taken of the objectives, financial situation or needs of any recipient of this presentation. Recipients of this presentation should carefully consider whether the securities issued by AB1 are an appropriate investment for them in light of their personal circumstances, including their financial and taxation position. Company Highlights Global developer and publisher of ASX AB1 mobile games with a portfolio of 358 titles, 130 million downloads, and an Share price $0.16 average of nearly 8 million monthly Shares on issue 118.3 million active users in Q1 2015. Market cap. -

IBM Infosphere

Software Steve Mills Senior Vice President and Group Executive Software Group Software Performance A Decade of Growth Revenue + $3.2B Grew revenue 1.7X and profit 2.9X + $5.6B expanding margins 13 points $18.2B$18.2B $21.4B$21.4B #1 Middleware Market Leader * $12.6B$12.6B Increased Key Branded Middleware 2000 2006 2009 from 38% to 59% of Software revenues Acquired 60+ companies Pre-Tax Income 34% Increased number of development labs Margin globally from 15 to 42 27% 7 pts Margin 2010 Roadmap Performance Segment PTI Growth Model 12% - 15% $8.1B$8.1B 21% 6 pts • Grew PTI to $8B at a 14% CGR Margin • Expanded PTI Margin by 7 points $5.5B$5.5B $2.8B$2.8B ’00–’06’00–’06 ’06–’09’06–’09 Launched high growth initiatives CGRCGR CGRCGR 12%12% 14%14% • Smarter Planet solutions 2000 2006 2009 • Business Analytics & Optimization GAAP View © 2010 International Business Machines Corporation * Source: IBM Market Insights 04/20/10 Software Will Help Deliver IBM’s 2015 Roadmap IBM Roadmap to 2015 Base Growth Future Operating Portfolio Revenue Acquisitions Leverage Mix Growth Initiatives Continue to drive growth and share gain Accelerate shift to higher value middleware Capitalize on market opportunity * business • Middleware opportunity growth of 5% CGR Invest for growth – High growth products growing 2X faster than rest of • Developer population = 33K middleware Extend Global Reach – Growth markets growing 2X faster than major markets • 42 global development labs with skills in 31 – BAO opportunity growth of 7% countries Acquisitions to extend -

IBM Zec12 Processor Subsystem the Foundation for a Highly Reliable, High Performance Mainframe SMP System

IBM zEC12 Processor Subsystem The Foundation for a Highly Reliable, High Performance Mainframe SMP System Robert Sonnelitter System z Processor Development, Systems & Technology Group, IBM Corp. [email protected] © 2013 IBM Corporation Smarter Systems for a Smarter Planet IBM zEC12 Processor Subsystem . Historical Background . Performance Characteristics . CP/L3 Design Highlights . SC/L4 Design Highlights . System RAS Features 2 © 2013 IBM Corporation Smarter Systems for a Smarter Planet System z Shared Cache History . 1990 – Fully shared second level cache . 1995 – Cluster Shared L2 . 1997 – Distributed Cache Topology . 1998 – Bi-Nodal Distributed Cache Design . 2003 – Modular Nodal Design, Ring Topology . 2008 – Three Level Cache Hierarchy, Fully Connected Topology . 2010 – Four Level Cache Hierarchy, eDRAM Caches 1990 1993 1995 1994 1995 1996 1997 1998 1999 2000 2003 2005 2008 2010 2012 H2 H5 H6 G1 G2 G3 G4 G5 G6 z900 z990 z9 z10 z196 zEC12 6w 6w 10w 6w 10w 10w 10w 10w 12w 20w 32w 54w 64w 80w 101w 3 © 2013 IBM Corporation Smarter Systems for a Smarter Planet Customer Environment & Workload Characteristics . Highly virtualized workloads – Heavily shared system environment – Sustained high processor utilizations – Tasks dynamically dispatched across the system . Large single image workloads . High data sharing across processors . Response time sensitive workloads . Large memory footprint . Extremely high system reliability . zOS, zVM, zVSE, TPF, zLinux operating systems 4 © 2013 IBM Corporation Smarter Systems for a Smarter Planet Performance Benchmarks System Capacity . Ensure Per-Thread and SMP 5 Performance growth with increased 4 system capacity 3 . Guaranteed customer performance 2 targets with constant software 1 z9 z10 z196 zEC12 90nm 65nm 45nm 32nm . -

Z/OSMF Security Setup Overview V2R3 / V2R4 Session 26893

z/OSMF Security Setup Overview V2R3 / V2R4 Session 26893 Julie Bergh [email protected] 1 Abstract The setup and security configuration for z/OSMF has greatly improved and been simplified over time. Fine out what improvements have been made to get z/OSMF set up and running securely under z/OS V2R3 and V2R4 so that one can take advantage of this powerful modernization tool. User experiences will be discussed in managing setup and configuration, highlighting success and problem areas. Other z/OSMF sessions at Share. Introduction Background 2 What is z/OSMF • IBM z/OS Management Facility (z/OSMF) provides system management functions in a task-oriented, web browser-based user interface with integrated user assistance, so that you can more easily manage the day-to-day operations and administration of your mainframe z/OS systems. By streamlining some traditional tasks and automating others, z/OSMF can help to simplify some areas of z/OS system management. • z/OSMF allows you to communicate with the z/OS system through a web browser, so you can access and manage your z/OS system from anywhere. Multiple users can log into z/OSMF using different computers, different browsers, or multiple instances of the same browser. NewEra – Link to eBook Securing z/OSMF https://www.newera-info.com/eBooks.html 4 What is z/OSMF • z/OSMF provides a framework for managing various aspects of a z/OS system through a web browser interface. • z/OSMF provides you with a single point of control for: • Viewing, defining, and updating policies that affect system behavior • Monitoring the performance of the systems in your enterprise • Managing software that runs on z/OS • Performing problem data management tasks • Consolidating your z/OS management tools. -

Rob Weir Robert [email protected]

IBM Lotus Symphony Rob Weir http://symphony.lotus.com [email protected] 14:38:03 1 Why Move to IBM® Lotus® SymphonyTM? ● Symphony is based on Open Standard = No vendor lock in ● IBM's Office Productivity Suite – Built For “The Majority Of Users” – Lotus Symphony Documents – Lotus Symphony Presentations – Lotus Symphony Spreadsheets – Supports 28 Languages + Strong Accessibility Support – EclipseTM Based And Supports JavaTM, UNO & LotusScript® Dev ● Simple and Flexible ● Free and Supported ● Easy to use interface ● Free To All ● Plugin extension and SDK ● Support Options ● Integrated in Lotus® NotesTM 8 – Web Only ● – Fee Based Support Client flexibility, Easy to deploy – Support Included With NotesTM Client 14:38:03 2 How does Symphony differ from OpenOffice.org? ● Usability ● Enhanced sidebar UI ● Enhanced Data Pilot UI ● Interoperability (200 bugs fixed) ● Enhanced ODF backward compatibility ● Enhanced Office 2007 format file import ● Better VBA support ● Performance ● Document asynchronous loading ● Document quick saving ● IAccessible2 support 14:38:03 3 PC Magazine: “Editor's Choice” http://www.pcmag.com/article2/0,2817,2387439,00.asp 14:38:03 4 IBM Mobile Viewer ● ODF document (.odp/.odt/.ods) viewing application for Android, iOS devices ● Opening files located in file system (e.g. on sd card), weblink, Dropbox, or email attachment ● High performance ● High fidelity (meta files wmf/emf/svm supported) ● Native application and user experience 14:38:03 5 Introducing LotusLive Symphony More than editors through a browser ● Co-editing -

IBM Lotuslive™ Meetings the Smart Choice!

™ IBM LotusLive Meetings The smart choice! With IBM LotusLive Meetings, online collaboration has never been easier or smarter. Whether a colleague is working from home or a client Benefits is half way around the world, ideas and information • Easy to use interface lets you to set up and run need to pass freely and in real-time. That’s why you your own meetings need LotusLive Meetings, a full-featured online meeting service that integrates Web and video conferencing. • Single point of management for video and Web conferencing service You can pull together a Web conference on the fly for one or hundreds – all with the same account. • A waiting room feature for early web conference With IBM LotusLive Meetings, you can share your attendees desktop, conduct demos and deliver presentations • Security-rich service via HTTPS and is encrypted effortlessly, without ever leaving home. LotusLive with 128-bit SSL Meetings lets you set up a meeting wherever - and whenever - you want. All you need is a Web browser. • “Publish” support of a wide variety of document formats, including open document format (ODF), “LotusLive Meetings has changed the portable document format (PDF) files, and Microsoft Office formats way we do business...we no longer • Support of translation in the service for 9 have to have our adjusters travel in languages*, with the ability to host and join order to have meetings. It has greatly conferences in your preferred language. increased our production, as a result.” • Easy to set up and attend with one permanent meeting ID - Susan Cruz, Lozano Insurance Adjusters • Accessible anytime, anywhere through a Web browser LotusLive Meetings will give you a whole new way of doing business by using a Software as a Service • No downloads for participants – fewer meeting (SaaS) model to deliver the collaboration services you delays need when you need them. -

Chairman's Letter

2012 Corporate Responsibility Report ibm.com/ibm/responsibility/2012 Chairman’s Letter In this section, Chairman, President and Chief Executive Officer Ginni Rometty’s letter describes how IBM’s goal to unite its business and citizenship strategies is taking shape. We take a thoughtful, comprehensive approach to corporate responsibility and corporate citizenship at IBM, and we integrate that approach into many aspects of our company. 2 A LETTER FROM VIRGINIA M. ROMETTY Chairman, President and Chief Executive Officer Innovation that matters Five years ago, we began a conversation with the world about building a Smarter Planet. It was based on what we were seeing with clients and stakeholders around the world, as a new era of technology and global integration unleashed an unprecedented volume, velocity and variety of data. We believed this so-called “Big Data” constituted nothing less than a new natural resource. What steam power, electromagnetism and fossil fuels were to earlier eras, data could be to ours. It held the potential to unleash new levels of prosperity and societal progress. Since then, we have been working with clients, partners, academic peers, government leaders and other constituencies to mine and apply that resource—helping to make healthcare more accessible, education more effective, food safer, transportation more reliable and cities more livable. We have also applied analytics, social networks and cloud infrastructure within our own company—making IBM more valuable and transparent, reducing our energy use, and improving our capacity to innovate for our clients and for the world. These are important goals—and you can read in this report how we measure our progress against them. -

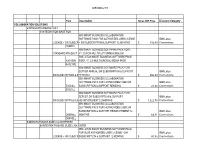

DIR-SDD-2111 Part Description Sirius DIR Price Discount Category

DIR-SDD-2111 Part Description Sirius DIR Price Discount Category COLLABORATION SOLUTIONS B INTEGRATION BASE FOR I B INTEGRATION BASE FOR I IBM SMART BUSINESS COLLABORATION SOFTWARE PACK FOR AUTHORIZED USER LICENSE IBM Lotus LICENSE + SW SUBSCRIPTION+ SW SUBSCRIPTION & SUPPORT & SUPPORT 12 MONTHS $ 116.49 Connections D05PPLL IBM SMART BUSINESS SOFTWARE PACK FOR I, STANDARD PRODUCT V1.1.0 FOR MULTIPLATFORMS ENGLISH IBM LOTUS SMART BUSINESS SOFTWARE PACK AJ01XEN FOR I, V1.2.0 MULTILINGUAL MEDIA PACK AJ021ML IBM SMART BUSINESS SOFTWARE PACK FOR I SERVER ANNUAL SW SUBSCRIPTION & SUPPORT IBM Lotus SW SUBSCRIPTION & SUPPORTRENEWAL RENEWAL $ 406.49 Connections IBM SMART BUSINESS COLLABORATION SOFTWARE PACK FOR I AUTHORIZED USER SW IBM Lotus E05L0LL SUBSCRIPTION & SUPPORT RENEWAL $ 23.34 Connections E05L1LL IBM SMART BUSINESS SOFTWARE PACK FOR I SERVER SW SUBSCRIPTION & SUPPORT IBM Lotus SW SUBSCRIPTN & SUPTREINSTATEMENT REINSTATEMENT 12 MONTHS $ 1,222.78 Connections IBM SMART BUSINESS COLLABORATION SOFTWARE PACK FOR I AUTHORIZED USER SW SUBSCRIPTION & SUPPORT REINSTATEMENT 12 IBM Lotus D05PNLL MONTHS $ 69.81 Connections D05PQLL B INTEGRATN BASE SUSE LNX ENTRPRISE B INTEGRATN BASE SUSE LNX ENTRPRISE IBM LOTUS SMART BUSINESS SOFTWARE PACK FOR SUSE AUTHORIZED USER LICENSE + SW IBM Lotus LICENSE + SW SUBSCRIPTIONSUBSCRIPTION & SUPPORT & SUPPORT 12 MONTHS $ 80.35 Connections DIR-SDD-2111 D0BXGLL IBM SMART BUSINESS SOFTWARE PACK FOR SUSE LINUX ENTERPRISE SERVER V1.1.0 ENGLISH MEDIA STANDARD PRODUCT PACK AJ01YEN IBM SMART BUSINESS SOFTWARE PACK FOR